|

JESD204B��������ʵ�JEDEC�˜ʣ������D�Q���c����̎������֮�g�Ĵ��Д����ӿڡ����ǵ������˜ʣ���Q����ǰ�汾��һЩȱ�ݡ�ԓ�ӿڵă��ݰ����������ӿ�·�������·����g���٣������c���֕r��Ҫ����ͣ��Լ��D�Q����߉�����ķ��b��С����ҹ����̵�����ģ�M/�����D�Q�����ô˽ӿڣ�����ADI��˾�� AD9250 ��

�c�F�нӿڸ�ʽ�ͅf�h��ȣ�JESD204B�ӿڸ����s�������횿˷�һЩ���y���܌��F�䃞�ݡ����κ������˜�һ�ӣ�Ҫʹԓ�ӿڱȆα��������ʻ��p����������CMOS/LVDS�ȳ��ýӿڸ��ܚgӭ��������ܟo�p�ع������mȻJESD204B�˜���JEDEC�ƶ�����ijЩ�ض���Ϣ����Ҫ�U�������߿���ɢ���ڶ��������īI�С����⣬�����һ��������ָ���ܸ�Ҫ�f��ԓ�˜ʡ�����ԭ���Լ�����ų����ϣ��o�Ɍ�ʹ���ߌ��O���Ў�����

�����U�JESD204B�˜ʵ�ADC�cFPGA�Ľӿڣ�����Д����Ƿ������������Լ����ܸ���Ҫ���ǣ�������І��}�r�ų����ϡ�����ӑՓ�Ĺ����ų����g���Բ��ó��õĜyԇ�c�y���O�䣬����ʾ������߉�����x���Լ�Xilinx®��ChipScope��Altera®��SignalTap��ܛ�����ߡ�ͬ�r�U���˽ӿ���̖��ݔ���Ա��܉�����һ�N���N�������F��̖��ݔ�Ŀ�ҕ����

JESD204B����

JESD204B�˜��ṩһ�N��һ������������D�Q���c������̖̎�������ӿڵķ�����ͨ����ADC��DAC�cFPGA�ӿڣ��������ͨ���IJ��Д�����ݔ���@��һ�N�����ٶȵĴ��нӿڡ�ԓ�ӿ��ٶȸ��_12.5 Gbps/ͨ����ʹ�Î����Д����·��Ƕ��ʽ�r犺͌��R�ַ������p��������֮�g���߾��������������߾�ƥ��Ҫ�������˽����c���֕r��s�����}���Ķ������˸����D�Q�������ӿڵČ�ʩ�������·��Ҫ�ڔ�����ݔ֮ǰ��������˴����µ����𣬱�횲����µļ��g���_���ӿ��Ƿ������������Լ��ڽӿڹ��ϕr��ô�k��

JESD204B�ӿ�ͨ�^�����A������ͬ���·�����a�Mͬ��(CGS)����ʼͨ��ͬ��(ILAS)�͔�����ݔ�A�Ρ��·��Ҫ������̖�����텢���r犣������r犣�������һ�����CML���픵����B�ӣ��Q��“ͨ��”�����Լ�����һ������ͬ����̖��SYNC~�Ϳ��ܵ�SYSREF����ʹ����Щ��̖ȡ�Q�����

- ���0ʹ�������r犡�ͨ����SYNC~��

- ���1ʹ�������r犡�ͨ����SYNC~��SYSREF��

- ���2ʹ�������r犡�ͨ����SYNC~��

���0���S����r�����ԝM����������DZ��ĵ����c�����1�����2�ṩ�˽����_�������t�ķ������@����Ҫͬ��������������Ҫϵ�yͬ����̶����t�đ����зdz���Ҫ������һ��ϵ�y��ij���¼���Ҫ��֪�IJɘ��أ�����ij���¼������Ҏ���r�g��푑�ݔ����̖��

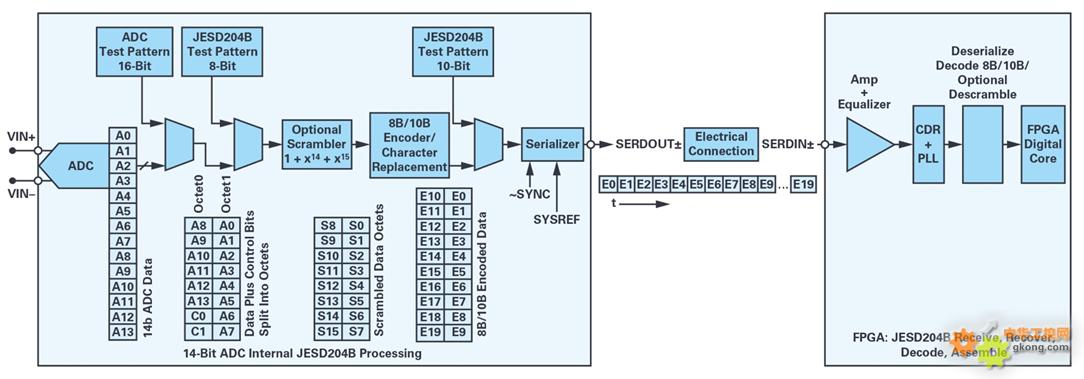

�D1�@ʾ�ˏİl������(ADC)����������(FPGA)�ĺ���JESD204B�·��������һ��ADC����һ��ͨ����ݔ��

�mȻJESD204BҎ�����S��׃������ijЩ׃�������·�Ľ����e��Ҫ���@Щ�P�I׃��������ʾ��ע���@Щֵͨ����ʾ��“X − 1”����

- M���D�Q������

- L������ͨ������

- F��ÿ����8λ�ֹ�����

- K��ÿ�������Ď�����

- N��N’���քe��ʾ�D�Q���ֱ��ʺ�ÿ���ӱ�ʹ�õ�λ����4�ı�������N’��ֵ����Nֵ���Ͽ��ƺ���䔵��λ����

���0��ͬ�����E

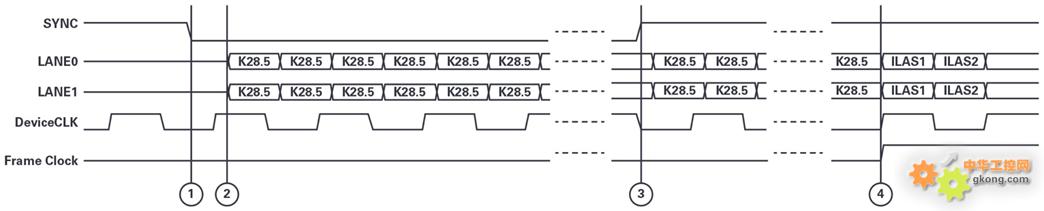

�����������S�����ÿ��Բ����������ε����0����ģʽ���@Ҳ�ǽ�������C�·�����ģʽ�����0ͨ�^�����A�������ͱO��ͬ����CGS�A�Ρ�ILAS�A�κ͔����A�Ρ����A�����P�ĈD���Բ�ͬ��ʽ�@ʾ������������ʾ������߉�����x��FPGA̓�MI/O�����x����Xilinx ChipScope��Altera SignalTap�����^�쵽�@Щ������

���a�Mͬ��(CGS)�A��

�������·���^�쵽��CGS�A������Ҫ������D2��ʾ���D��5��ͻ���@ʾ���c�f�����¡�

- ������ͨ�^����SYNC~���_���l��һ��ͬ��Ո��

- �հl������һ����̖�_ʼ���l��δ�Ӕ_��/K28.5/��̖��ÿ����̖10λ����

- ���������յ�����4���o�e�`���B�m/K28.5/��̖�rͬ����Ȼ��SYNC~���_���ߡ�

- ��������횽��յ�����4���o�e�`8B/10B�ַ�����tͬ����ʧ�����·����CGS�A�Ρ�

- CGS�A�νY����ILAS�A���_ʼ��

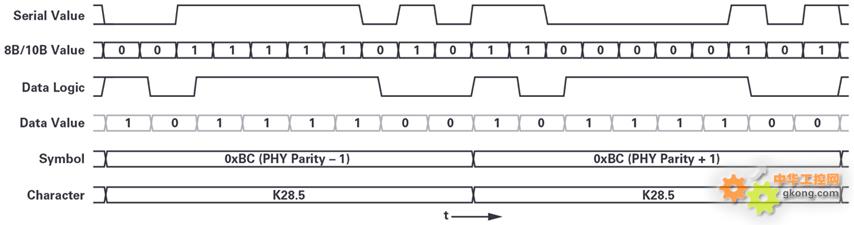

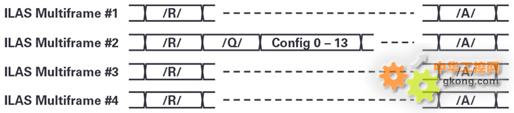

/K28.5/�ַ���JESD204B�˜���Ҳ�Q��/K/����D3��ʾ���˜�Ҫ��ֱ��ƽ�⡣����8B/10B���a�����Ԍ��Fƽ������������1��0��ƽ�����С�ÿ��8B10B�ַ����ܾ�������1�^�ࣩ��ؓ��0�^�ࣩƫ���ǰ�ַ�����ż������ǰ�l�͵��ַ��ĘO��ƫ��Q�����@ͨ����ͨ�^����l������ż�����cؓ��ż���ց팍�F���D���@ʾ��/K28.5/��̖�ăɷN�O�ԡ�

�D1.JESD204B�·�D��һ��ADCͨ�^һ��ͨ���cFPGA�ӿ�

�D2.JESD204B���0�·��̖��CGS�A�ε�߉ݔ�������O�Ѓɂ�ͨ����һ���������ɂ�ADC��

�D3.K28.5�ַ���߉ݔ���Լ������ͨ�^JESD204B Tx��̖·������

���cע�������c��

- ����ֵ��ʾͨ�^ͨ����ݔ��10λ��߉�ƽ����ͨ�^�y�������ӿڵ�ʾ����������

- 8B/10Bֵ��ʾͨ�^ͨ����ݔ��߉ֵ��10λ������ͨ�^�y�������ӿڵ�߉�����x������

- ����ֵ�͔���߉��ʾ8B/10B���aǰJESD204B�հl��ģ�K�ȷ�̖��߉�ƽ����ͨ�^Xilinx ChipScope��Altera SignalTap��FPGA߉�������߿�����

- ��̖��ʾҪ�l�͵��ַ���ʮ���M��ֵ��ע��PHY�ӵ���ż�ԡ�

- �ַ���ʾJEDECҎ������ָ��JESD204B�ַ���

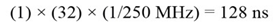

ILAS�A��

ILAS�A����4�����������S���������R���������·��ͨ�����Լ���C�·�����������{�Ͳ�ͬ�L�ȵ��߾��Լ����������µ��ַ�ƫб��ͨ����회��R��4�������o�o���B���D4�����oՓ���üӔ_�·�����c��ILASʼ�K�ǟo�Ӕ_��ݔ��

SYNC��̖�ĵ��ƽ׃����ƽ���M��ILAS�A�Ρ��l��ģ�K�Ȳ���ۙ����ADC�Ȳ���һ�������������_ʼ�l��4����������������ַ��в�����䔵�����Ա���������Ķ������D4����4������������

- ����1����/R/�ַ�[K28.0]�_ʼ����/A/�ַ�[K28.3]�Y����

- ����2����/R/�ַ��_ʼ�����/Q/ [K28.4]�ַ���Ȼ����14������8λ�ֵ��·���Å�������1���������/A/�ַ��Y����

- ����3���c����1��ͬ��

- ����4���c����1��ͬ��

-

���L�ȿ�������JESD204B����Ӌ�㣺

(S) ×��1/�ɘ����ʣ���

���x��

���ӱ���/�D�Q��/����×��1/�ӱ����ʣ�

ʾ����

�ɘ����ʞ�250 MSPS��ÿ��ÿ�D�Q��һ���ӱ����D�Q����ע���ڱ�����“S”��0������������a����M��ֵ-1�����䎬�L�Ȟ�4 ns��

(1) (1)

�����L�ȿ�������JESD204B����Ӌ�㣺

(2) (2)

���x��

���ӱ���/�D�Q��/����×������/������×��1/�ɘ����ʣ�

ʾ����

�ɘ����ʞ�250 MSPS��ÿ��ÿ�D�Q��һ���ӱ���ÿ������32�����D�Q����������L�Ȟ�128 ns��

(3) (3)

�����A�Σ�ʹ���ַ���Q��

�ڔ�����ݔ�A�Σ�ͨ�^�����ַ��O�؎����R���ڎ��ĽYβ̎�����ַ���Q���ڔ����A�Σ��������R��������~���_�N���ַ���Q���S�ڎ�߅��̎�l�͌��R�ַ���Ψһ�l���Ǯ�ǰ�������һ���ַ�������Q����һ�������һ���ַ����@�����ڣ��g�_�J��ILAS���к��Rδ��׃��

���F������r�r�������l���������ַ���Q��

- �������˼Ӕ_��������������һ��8λ�ֵ�����һ����8λ�֡�

- ��ʹ���˼Ӕ_�����������һ��8λ�ֵ���0x7C�������һ��8λ�ֵ���0xFC��

�l�����ͽ��������Ա���һ�����ض���Ӌ����(LMFC)�������mӋ����(F × K) − 1��Ȼ���@�ص�“0”�����_ʼӋ�������ԃȲ������������аl�����ͽ������l��һ��������Դ��SYSREF���@Щ��������SYSREF��λ��LMFC���@������LMFC������ͬ������һ���r����ڃȣ���

ጷ�SYNC���������������������l��������һ��(Tx) LMFC�@��0�r�_ʼILAS�����F × K�O���m��������(�l�������a�r�g)+(��·�����r�g)+(��������a�r�g)���t���Ք���������һ��LMFC֮ǰ�Ľ�������SERDES������ȥ�����������є�������FIFO��Ȼ������һ��(Rx) LMFC߅���_ʼݔ���������l������SERDESݔ��ͽ�����FIFOݔ��֮�g���@�N��֪�Pϵ�Q���_�������t��

�D4.JESD204B ���0�·��̖��ILAS�A�ε�߉ݔ��

�D5./K/�ַ�[K28.5]��/R/�ַ�[K28.0]��/A/�ַ�[K28.3]��/Q/�ַ�[K28.4]�D

��1.ILAS����2��CONFIG����14��JESD204B���Å���8λ�֣�

|

8λ�֔�

|

λ7 (MSB)

|

λ6

|

λ5

|

λ4

|

λ3

|

λ2

|

λ1

|

λ0 (LSB)

|

|

0

|

DID[7:0]

|

|

1

|

ADJCNT[3:0]

|

BID[3:0]

|

|

2

|

|

ADJDIR

|

PHADJ

|

LID[4:0]

|

|

3

|

SCR

|

L[4:0]

|

|

4

|

F[7:0]

|

|

5

|

|

K[4:0]

|

|

6

|

M[7:0]

|

|

7

|

CS[1:0]

|

N[4:0]

|

|

8

|

SUBCLASS[2:0]

|

N[4:0]

|

|

9

|

JESDV[2:0]

|

S[4:0]

|

|

10

|

HD

|

CF[4:0]

|

|

11

|

RESERVED 1

|

|

12

|

RESERVED 2

|

|

13

|

FCHK[7:0]

|

����������e��

JESD204B�����f��һ�����s�Ľӿژ˜ʣ����������S����֮̎��Ҫ�ҳ���������������ԭ����Ҫ�����ܵ����������õ��˽⣺

����CGSģʽ�����SYNC����߉���ƽ�������}�_���ƽ���m�r�g����4��������

�z���·�壬����늣�

- SYSREF��SYNC~��̖��ֱ����ϡ�

- ���·��δ��늵���r�£��z���SYNC~Դ��ͨ������FPGA��DAC����SYNC~ݔ�루ͨ����ADC��FPGA�����·��SYNC~�B���Ƿ������Ҿ��е��迹��

- �_��������������費����̖��ݔ���������أ����磺ֵ̫С���·�͕����o�����_�ӡ�

- �_�JJESD204B�·�IJ���߾�������|����ʹ�ã�ƥ�䡣

- �_�J�߾��IJ���迹��100 Ω��

�z���·�壬��늣�

- ���SYNC·������һ�����_��/�D�Q�����_��������������

- �_�JSYNC~Դ�Ͱ����·��SYNC+��SYNC-�������֣��������_���a������SYNC~��������Ҫ���߉�ƽ�����߉�ƽ�����ݣ����z��Դ�ͽ����������ҳ����}����t��Ո��ԃ���������̡�

- �_�JJESD204B���аl�����Ͱ��·�������_���a������JESD204B���Д���������Ҫ������_߉�ƽ�����߉�ƽ�����ݣ����z���·�ā�Դ�ͽ����������ҳ����}����t��Ո��ԃ���������̡�

�z��SYNC~��̖��

- ���SYNC~���o�B߉�ƽ���·��ͣ����CGS�A�Ρ����������l�͵Ĕ����І��}������JESD204B������δ���ӱ��M�����_��a���_�J�l�͵���/K/�ַ����_�J���������O�ã��_�JSYNC~Դ���z����·�����]�^�SYNC~��̖�������·�M��ILASģʽ���Ķ��ҳ��·���������հl�����}����t��Ո��ԃ���������̡�

- ���SYNC~���o�B߉���ƽ���_�JԴ�����Ƿ����_������SYNC~߉�ƽ���z��������������衣

- ���SYNC~�}�_׃����ƽ��Ȼ��߉���ƽ��B�ҳ��m�r�g����6���������ڣ��tJESD204B�·����CGS�A��ǰ�M��ILAS�A�Σ�����ͣ���ں�һ�A�Ρ��@������ζ��/K/�ַ����_��CDR�Ļ�������������Ո���“ILAS�����ų�”���֡�

- ���SYNC~׃����ƽ�ҳ��m�r�g����6���������ڣ��t�·����ILAS�A��ǰ�M�������A�Σ������ں�һ�A�ΰl�����ϣ����P�����ų���ʾՈ���“�����A��”���֡�

�z�鴮�Д���

- �_�J�հl���Ĕ����ٶȺͽ��������A�������Ƿ���ͬ��

- �ø��迹̽�^��������ܣ�ʹ�ò��̽�^���y��ͨ��������ַ��������e�`���_��ͨ������߾�ƥ�䣬PCB�ϵķ���·��δ�Д࣬�����������_���ӵ�PCA�ϡ��cILAS�͔����A�εģ����ƣ��S�C�ַ���ͬ��CGS�ַ���������ʾ�������R�e�����ʹ���ٶ����ߵ�ʾ��������

- �ø��迹̽�^��C/K/�ַ���

- ���/K/�ַ����_���t��ʾ�·���հl���˹���������

- ���/K/�ַ������_���t��ʾ�հl���������·��ͨ����̖�І��}��

- ����ֱ����ϣ��_�J�l�����ͽ�������ģ늉���������Ҫ���ȡ�

- ������ʩ��r���l������ģ늉��������ܞ�490 mV��1135 mV��

- ������ʩ��r����������ģ늉��������ܞ�490 mV��1300 mV��

- �_�J����ͨ���ϵİl����CML���늉���ע�⣬CML���늉�������̖����늉��[���ăɱ�����

- ����3.125 Gbps�����µ��ٶȣ��l����CML���늉�������0.5 V p-p��1.0 V p-p��

- ����6.374 Gbps�����µ��ٶȣ��l����CML���늉�������0.4 V p-p��0.75 V p-p��

- ����12.5 Gbps�����µ��ٶȣ��l����CML���늉�������0.360 V p-p��0.770 V p-p��

- �_�J����ͨ���ϵĽ�����CML���늉���ע�⣬CML���늉�������̖����늉��[���ăɱ�����

- ����3.125 Gbps�����µ��ٶȣ�������CML���늉�������0.175 V p-p��1.0 V p-p��

- ����6.374 Gbps�����µ��ٶȣ�������CML���늉�������0.125 V p-p��0.75 V p-p��

- ����12.5 Gbps�����µ��ٶȣ�������CML���늉�������0.110 V p-p��1.05 V p-p��

- ��������A�����x헣�������ԓ�x헲��^�씵��·���ϵĔ�����̖��

- �_�J�l�����c��������M��Lֵһ�£���t�������ʿ��ܲ�ƥ�䡣���磬M=2��L=2�@�N��r���A�ڴ��нӿڔ���������M=2��L=1�@�N��r��һ�롣

- �_���M��l�����ͽ������������r����i�����l�����_��

���SYNC׃����ƽ�ҳ��m�s4���������tͣ����ILASģʽ��

- �·�����_ͻ

- �_�J�·����δƫ��1���S������Ҏ����ֵ�p1����

- �_�JILAS�����������_���_�J�հl����������������ILAS�ڶ��������͵��·�������_��

- Ӌ���A��ILAS�L�ȣ�tframe, tmultiframe, 4 × tmultiframe�����_�JILAS�чLԇ��s4��������

- �_�J����ͨ�������������_�������ڶ�ͨ��/���·�_ͻ��

�M�딵���A�ε��·ż������λ���ȷ���CGS��ILAS�A�Σ����M�딵���A�Σ���

- �����Ի�϶������SYSREF��SYNC~��̖�Ľ����ͱ��֕r�g�oЧ��

- �·�����_ͻ��

- �ַ���Q�_ͻ��

- �Ӕ_���}��������ã���

- ͨ�������p�ġ����ӿ�����ʹ�ۈD�]�ϡ�

- �sɢ�r犻������r犵Ķ����^��

�P���ų��·���ϵ�����һ����ʾ��

- �����S������ٶ��\���D�Q�����·���@�ӾͿ���ʹ���^���@�õĵ͎����y���x����

- �O�����S������M��L��K��S�M��

- ���ܕrʹ�Üyԇģʽ

- ʹ�����0���ų�����

- �ų����ϕr���üӔ_

�������ų�ָ�ϲ�δ�F�M���п��ܣ�����ʹ��JESD204B�·�Լ�ϣ���˽������Ϣ�Ĺ��̎��ṩ��һ���ܺõĻ�����ܡ�

������JESD204BҎ���ĸ��������ṩ���·���P�Č�����Ϣ��ϣ���漰���@һ���¸����ܽӿژ˜ʵĹ��̎����Ы@�棬�����ų���������������

|