|

����

ģ��(sh��)�D(zhu��n)�Q��(ADC)�еIJɘӕ��a(ch��n)����B����ݷ��_���}������O(sh��)Ӌ�ˆTʹ�ÞV�������(q��)�ӷŴ�������Q�����@�֎�����һϵ�����P(gu��n)����(zh��n)�����������еȎ�����(y��ng)���У����F(xi��n)����ֱ���ͽ����������R����(zh��n)���O(sh��)Ӌ�ˆT��K���ò�����ϵ�y(t��ng)Ŀ��(bi��o)��

���Ľ�B�B�m(x��)�r�gΣ-Δ ADC��ͨ�^������̖朁���Ч��Q�ɘӆ��}�������@�N�����o��ʹ�ÿ���B�V�����;��_�������ɽ�Q�c�~��M�����P(gu��n)����̖�?zh��n)��{(di��o)�`���Ư�Ɔ��}���M���ɿsС��Q�����ߴ磬�����O(sh��)Ӌ��������ϵ�y(t��ng)����λƥ������w���t��

����߀���B�m(x��)�r�g�D(zhu��n)�Q���c�xɢ�r�g�D(zhu��n)�Q���M���˱��^�������ؽ�Bʹ���B�m(x��)�r�gΣ-Δ ADC��ϵ�y(t��ng)��(y��u)�ݺʹ��ڵ����ơ�

�ɘӻ���ԭ��

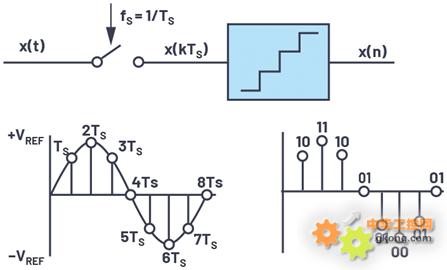

��(sh��)��(j��)��(sh��)�ֻ������ɘӺ������ɂ������^�̣���D1��ʾ���ɘ��ǵ�һ��������ʹ�òɘ��l��fS���B�m(x��)�r�g��׃ģ�M��̖x(t)�D(zhu��n)�Q���xɢ�r�g��̖x(n)����K�õ��� 1/TS (fS = 1/TS)�g������̖��

�D1.��(sh��)��(j��)�ɘ�

�ڶ��������������@Щ�xɢ�r�g�ӱ�ֵ�����һ��������ֵ�����Ô�(sh��)�ִ��a��ʾ����D1��ʾ���@�N������һ�M����ֵ�IJ�������(d��o)��(sh��)�ֻ��`��Q����������

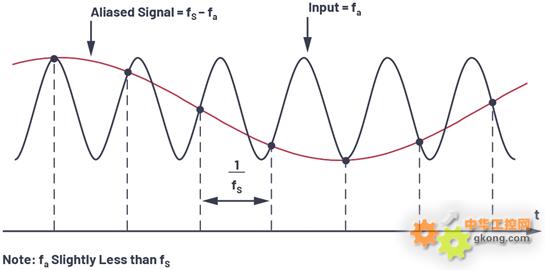

�ɘ��^��Ҳ����(d��o)�»�B�����Կ�����ݔ����̖�۷��Լ��ɘӱ��֕r��l���܇����F(xi��n)�C�����ο�˹��(zh��n)�tҪ��ɘ��l�ʱ�������������̖�l�ʵăɱ�������ɘ��l��С�����ģ�M��̖�l�ʵăɱ����������F(xi��n)һ�N�Q��"��B"�ĬF(xi��n)��

���������B�ڕr����l���еĺ��x�����ȁ����D2��ʾ�Ć���̖�����Ҳ��ɘ���̖�ĕr���ʾ���ڱ����У��ɘ��l�� fS���� fa������2����ֻ��������ģ�Mݔ���l�� fa����˲������ο�˹��(zh��n)�t��ע�⣬���H�ӱ��D�����a(ch��n)���^���l�� fS – fa�Ļ�B���Ҳ���

�D2.��B���r���ʾ

�D3.��B���l���ʾ

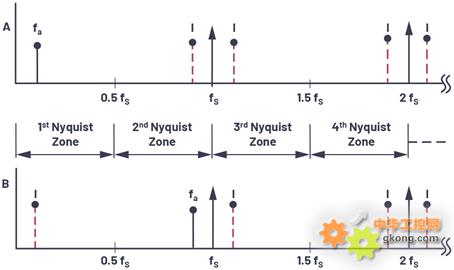

�@�N��r������(y��ng)�l���ʾ��D3��ʾ��

�ο�˹�؎������x���DC�� fS/2���l�V��ԓ�l�V�ɼ��֞�o��(sh��)���ο�˹�^(q��)��ÿ���^(q��)�Č��Ȟ� 0.5fS���ڌ��H��(y��ng)���У����Ԍ�����ɘ�����ADC���FFT̎���������档FFT̎�����H�ṩDC�� fS/2������(n��i)��ݔ��������һ�ο�˹�^(q��)���F(xi��n)����̖���B��

�������������}�_�ɘ������� fS �l���� fa �l�ʵĆ��l���Ҳ��M�вɘӣ�Ҋ�D1��������ٶ� fS > 2fa���ɘ������l��ݔ���@ʾ��ÿ�� fS����(sh��)�l�ʸ����������F(xi��n)ԭʼ��̖�Ļ�B���R�� |± KfS ± fa| �l��̎��K = 1,2,3,4�ȡ�

�������҂����]��һ�ο�˹�^(q��)֮�����̖���D3������̖�l�ʃH��С�ڲɘ��l�ʣ����LjD2�Еr���ʾ�����Ρ�ע�⣬��ʹ��̖λ�ڵ�һ�ο�˹�^(q��)֮�⣬���R���B�� fS – fa��λ��ԓ�^(q��)��(n��i)���ص��D3�������@������κ��R���l�� fa̎���F(xi��n)�ɔ_��̖����ôҲ�������F(xi��n)�� fa��������ڵ�һ�ο�˹�^(q��)��(n��i)�a(ch��n)���sɢ�l�ʳɷ֡�

��Q����(zh��n)�����F(xi��n)��������

���ڸ����ܑ�(y��ng)�ã�ϵ�y(t��ng)�O(sh��)Ӌ�ˆT��Ҫ��Q�ɘ��^�̌�(d��o)�µ�����������B���_�P(gu��n)���ݔ��ɘӆ��}���ɷN��͵ľ���ADC�����û����_�P(gu��n)��ݵIJɘӼ��g(sh��)��(g��u)�����@�ɷNADC�քe���ИI(y��)�г�Ҋ����αƽ��Ĵ���(SAR)��Σ-Δ ADC��

������

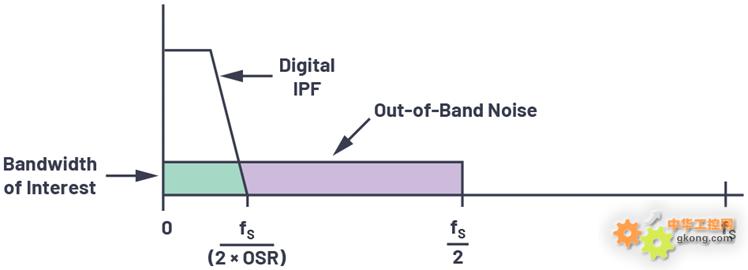

��������ο�˹��ADC�У�ADC��LSB��С���Q���M��ģ��(sh��)�D(zhu��n)�Q�r����ݔ���е����������@Щ���������ֲ��� fS/2����������(n��i)�����˽�Q���������}��������Ҫ�����^�ɘӼ��g(sh��)�����Դ�������ο�˹���l�ʵ����ʌ�ݔ����̖�M�вɘӣ�����������(SNR)�ͷֱ���(ENOB)���^�ɘ����g���x��ʹ�õIJɘ��l�ʞ��ο�˹���l�ʵ�N�� (2 × fIN)����˱����ͬ���������ֲ���N���ο�˹���l�ʷ�����(n��i)���@Ҳ���Ō�������B�V������Ҫ���^�ɘ���(OSR)���x�� fS/2fIN������ fIN ��Ŀ��(bi��o)��̖������һ����f����ADC�M��4���^�ɘӿ��~���ṩ1λ�ֱ��ʣ�������6 dB�ĄӑB(t��i)�����������^�ɘ��ʿɽ������w�������ӄӑB(t��i)����(DR)������^�ɘӞ�ΔDR = 10log10 OSR����λdB��

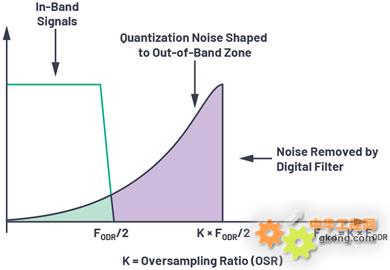

�^�ɘӿ����c���ɔ�(sh��)�֞V�����ͳ�ȡ����һ��ʹ�ú͌��F(xi��n)��Δ-Σ��ADC�����^�ɘ��{(di��o)�������������M�����Σ�ʹ��ֳ��F(xi��n)��Ŀ��(bi��o)�������⣬�Ķ����ӵ��l�µ����w�ӑB(t��i)��������D4��ʾ��Ȼ��(sh��)�ֵ�ͨ�V����(LPF)�V��Ŀ��(bi��o)�������������������ȡ������ݔ����(sh��)��(j��)���ʣ�ʹ��������ο�˹�����ʡ�

�D4.�^�ɘ�ʾ��

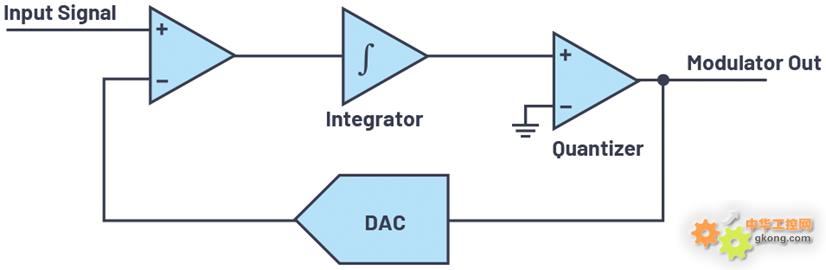

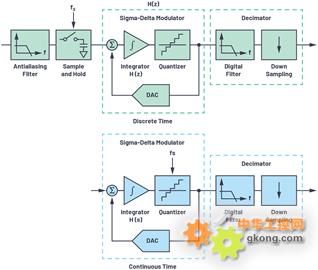

����������һ�N���ڽ����������ļ��g(sh��)����Σ-Δ ADC�У��ڭh(hu��n)·�V����֮��ĭh(hu��n)·��(n��i)ʹ�õͷֱ��ʣ�һλ����λ����������DAC����������������ȡݔ���е�������̖����D5��ʾ��

�D5.������

�e�������ۼ������`��������������������l�ʣ�Ȼ��ʹ�Ô�(sh��)�֞V�����M�ОV�����D6��ʾ����͵�Σ-Δ ADCݔ��x[n]�Ĺ����V�ܶ�(PSD)��������б��ȡ�Q�ڭh(hu��n)·�V�������A��(sh��)H(z)��Ҋ�D11����ÿʮ���l�̞�(20 × n) dB������n��ʾ�h(hu��n)·�V�������A��(sh��)��Σ-Δ ADCͨ�^�Y(ji��)��ʹ�������κ��^�ɘӣ��Ɍ��F(xi��n)����(n��i)�߷ֱ��ʡ�����(n��i)�������� fODR/2 ��ODR��ʾݔ����(sh��)��(j��)���ʣ���ͨ�^��߭h(hu��n)·�V�������A��(sh��)������^�ɘ��ʣ����ԫ@�ø��ߵķֱ��ʡ�

�D6.�^�ɘӺ������ΈD

��B

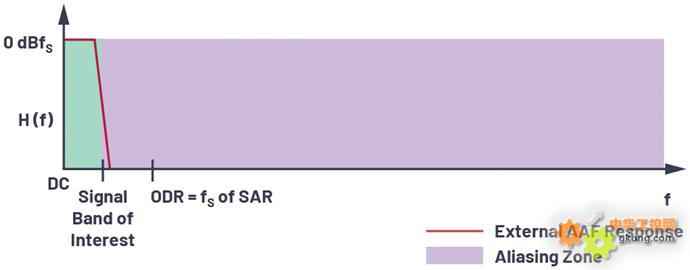

���˽�Q�����ܑ�(y��ng)���еĻ�B����ʹ�ø����A�Ŀ���B�V�����������κΔ�(sh��)���Ļ�B������B�V������һ���ͨ�V�������䎧��������ݔ����̖�����_����̖�в��������۷���Ŀ��(bi��o)����������l�ʷ������V�������܌�ȡ�Q�ڎ�����̖�cfS/2�Ľӽ��̶Ⱥ������˥�p����

����SAR ADC��ݔ����̖�����Ͳɘ��l��֮�g�IJ�ಢ���������҂���Ҫʹ�ø����A�ĞV�������@Ҫ����ø���(f��)�s�������A�ĞV�����O(sh��)Ӌ���ҹ��ʸ��ߣ�ʧ��������磬����ɘ��ٶȞ�200 kSPS��SAR��ݔ�뎧����100 kHz���t����B�V������Ҫ����>100 kHz��ݔ����̖���Դ_�������a(ch��n)����B���@����Ҫʹ�ØO���A�ĞV�������D7�@ʾ�˶��͵�����������

�D7.��BҪ��

����x��ʹ��400 kSPS�ɘ��ٶȁ����͞V�������A��(sh��)���t��Ҫ����>300 kHz��ݔ���l�ʡ���߲ɘ��ٶȕ����ӹ��ʣ�������F(xi��n)�p���ٶȣ���Ҫ�Ĺ���Ҳ�����������ڲɘ��l���h����ݔ�뎧��������Թ��ʞ���r�Mһ������^�ɘӕ��Mһ���Ō�����B�V������Ҫ��

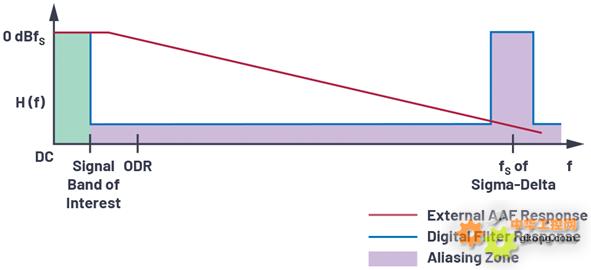

��Σ-Δ ADC�У��Ը��ߵ�OSR��ݔ���^�ɘӣ����ڲɘ��l���h����ݔ�뎧��������Ō��˿���B�V������Ҫ����D8��ʾ��

�D8.∑-Δ �ܘ�(g��u)�еĿ���B�V����Ҫ��

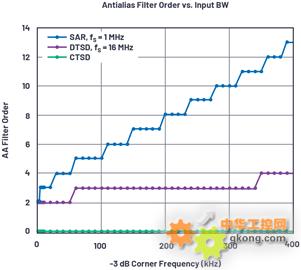

�D9�@ʾ��SAR���xɢ�r�gΣ-Δ(DTSD)�ܘ�(g��u)��AAF�ď�(f��)�s�̶ȡ�����҂�Ҫʹ��100 kHz –3 dBݔ�뎧���ڲɘ��l��fS���F(xi��n)102 dB˥�p���tDTSD ADC����Ҫʹ�ö��A����B�V������������SAR ADC�r�� fS �«@����ͬ˥�p���t��Ҫʹ�����A�V������

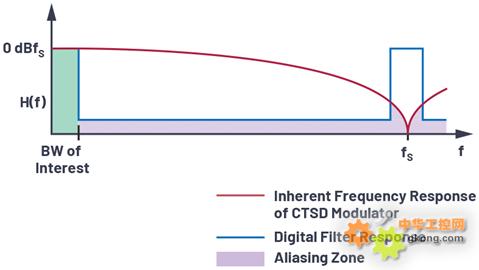

�����B�m(x��)�r�gΣ-Δ(CTSD) ADC������������˥�p���ܣ������҂��o��ʹ���κο���B�V������

�D9.���N�ܘ�(g��u)��AAF�V����Ҫ��

�@Щ�V������ϵ�y(t��ng)�O(sh��)Ӌ�ˆT���f�����y�}��������횃�(y��u)���@Щ�V�������Ա���Ŀ��(bi��o)�l����(n��i)�ṩ˥�p�����ұM�����ṩ���ߵ��������ܡ�����߀�������S�������`�����ʧ�{(di��o)�����桢��λ�`���ϵ�y(t��ng)�����M�����������ܡ�

���ң�������ADC�����Dz��ʽ�������҂���Ҫʹ���p����(sh��)���ğoԴ�M����Ҫ�ڶ�ͨ����(y��ng)���Ќ��F(xi��n)���õ���λƥ�䣬��̖��е����нM��Ҳ���ƥ�䡣��ˣ���Ҫʹ�ù������(y��n)��ĽM����

�_�P(gu��n)���ݔ��

�_�P(gu��n)���ݔ��ɘ�ȡ�Q������ϲɘ�ݔ��Ľ����r�g��������_�P(gu��n)�ɘ��_�P(gu��n)�r����Ҫ���/���˲�B(t��i)������@�Q��ݔ�뷴�_��Ҫ��ʹ��֧���@Щ˲׃�����ݔ���(q��)�ӷŴ��������⣬Ҫ���ڲɘӕr�g�Y(ji��)���r����ݔ�룬���Ҳɘ�ݔ��ľ��țQ��ADC�����ܣ���ζ���(q��)�ӷŴ�����Ҫ�ڷ��_�¼�����ٷ�(w��n)�������������Ҫʹ��֧�ֿ��ٽ������������_�P(gu��n)��ݲ������_�ĸߎ����(q��)���������_�P(gu��n)���ݔ���У�ÿ��(d��ng)�ɘ��_�����(q��)������������鱣������ṩ�Դ��ֻ�Ю�(d��ng)�(q��)�����߂����Ď��������r�����ܼ��r�ṩ�@�N��������������_�P(gu��n)�������ɘӕr�(q��)�����ϕ����F(xi��n)���_��������_����һ�βɘ�ǰδ�ܷ�(w��n)����������(d��o)�²ɘ��`��Ķ�Ӱ�ADCݔ�롣

�D10.�ɘӷ��_

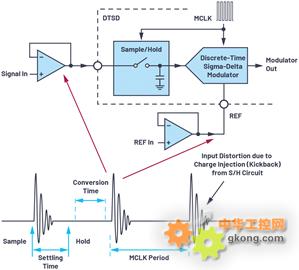

�D10�@ʾ��DTSD ADC�ϵķ��_�����磬����ɘ��l�ʞ�24 Mhz����ô��(sh��)��(j��)��̖��Ҫ��41 ns��(n��i)������������(zh��n)Ҳ��һ���_�P(gu��n)���ݔ�룬���Ի���(zh��n)ݔ�����_��Ҳ��Ҫһ���ߎ������_�����@Щݔ����̖�ͻ���(zh��n)늉����_��Ҳ����������ʹ��̖朵����w�����½������⣬ݔ����̖�(q��)������ʧ���������S&H�l�ʸ��������Mһ����߿���BҪ�����_�P(gu��n)���ݔ�룬�ɘ��ٶȵ�׃������(d��o)��ݔ�����׃�����@���܌�(d��o)�������{(di��o)�Cϵ�y(t��ng)���Ԝp���(q��)��ADC�r�(q��)������ǰһ���a(ch��n)���������`�

�B�m(x��)�r�gΣ-Δ ADC

CTSD ADC����һ�NΣ-Δ ADC�ܘ�(g��u)�������^�ɘӺ������ε�ԭ�������ṩ��һ�N��ʩ�ɘӵķ����������@����ϵ�y(t��ng)��(y��u)�ݡ�

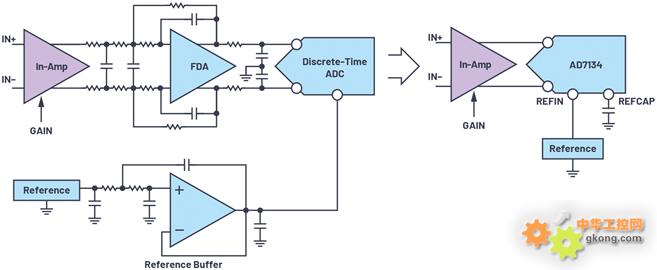

�D11��DTSD�ܘ�(g��u)��CTSD�ܘ�(g��u)�M���˱��^�����Կ�����DTSD�ܘ�(g��u)�ڭh(hu��n)·֮ǰ��ݔ��ɘӡ��h(hu��n)·�V����H(z)�ڕr�g�����xɢ�ģ���ʹ���_�P(gu��n)��ݷe�������F(xi��n)������DACҲ�ǻ����_�P(gu��n)��ݡ������M��ݔ��ɘӕ���(d��o)��fS�Юa(ch��n)����B���}�����Ԍ�ݔ��ɘ�֮ǰ��Ҫ��ݔ���ʹ�ÿ���B�V������

�D11.�xɢ�r�g���B�m(x��)�r�g�{(di��o)������D

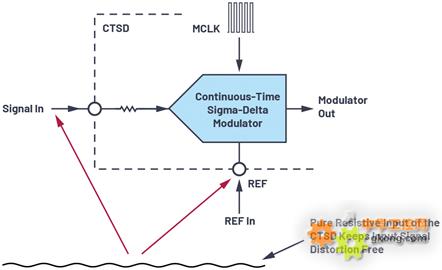

CTSDδ��ݔ������òɘ����������ڭh(hu��n)·��(n��i)���������ϲɘӡ��h(hu��n)·�V����ʹ���B�m(x��)�r�g�e�������F(xi��n)�˕r�g�B�m(x��)�ԣ�����DACҲ����ˡ��c�������ܵ�����һ�ӣ���ɘӌ�(d��o)�µĻ�BҲ�������Ρ��ɴ˵ó��ˎ��o�ɘӻ�B��ADC��ʹ���Գ����

CTSD�IJɘ��l���ǹ̶��ģ��@�cDTSD��ͬ�����ߵ��{(di��o)�����ɘ��l�ʿ����p�ɔUչ�����⣬CTSD ADC�����ӵ����̶̳�Ҳ�����_�P(gu��n)���ADC���F(xi��n)�ɵľ��w��CMOS��ʎ����ADC�ṩ���صͶ��ӕr犣������ڱ����ڸ��x��B(t��i)��ݔ?sh��)Ͷ��ӕr犣�������EMC��

CTSD���Ѓɴ�(y��u)�ݣ����������л�B�������������Ҟ���̖�ͻ���(zh��n)�ṩ����ݔ�롣

���еĿ���B����

���������Ƶ��h(hu��n)·��(n��i)���a(ch��n)�����еĻ�B���ơ���D12��ʾ��ݔ����̖�ڲɘ�ǰͨ�^�h(hu��n)·�V���������������Ϯa(ch��n)�����۷�����B���`��Ҳ����(j��ng)�˞V����ȥ������̖�ͻ�B�`���cΣ-Δ�h(hu��n)·������ͬ�������f����(sh��)��������Σ-Δ�ܘ�(g��u)�Ќ�ʩ�c���������Ƶ������Ρ���ˣ�CTSD�h(hu��n)·���l��푑�(y��ng)��Ȼ�����Ƽs��ɘ��l������(sh��)����ݔ����̖���䮔(d��ng)����B�V���������á�

�D12.CTSD�{(di��o)�������l��푑�(y��ng)

����ݔ��

�c�ɘӱ���������ȣ�����̖�ͻ���(zh��n)ݔ���в�������ݔ����������(q��)�ӡ��ṩ�㶨����ݔ��r�������a(ch��n)�����_��������ȫ�Ƴ��(q��)������ݔ�벻���a(ch��n)��ʧ�棬��D13��ʾ���������ݔ���迹�㶨��׃��Ҳ�o���������`�������{(di��o)�Cϵ�y(t��ng)��

�D13.CTSD��ݔ�뽨��

��ʹADC�ṩ�ΘO���Դ��ģ�Mݔ��Ҳ�������p�O�Եġ���˟o�����p�Oǰ�˺�ADC֮�g��ʩ�ƽ�D(zhu��n)�Q��ADC��ֱ�����ܿ����cݔ�����F(xi��n)�ھ���ݔ�빲ģ���P(gu��n)�����ݔ������r����r��ͬ��

����(zh��n)ؓ(f��)�dҲ�������ԣ����Ԝp���_�P(gu��n)���_����˟o��ʹ�ÆΪ��Ļ���(zh��n)늉����_������ͨ�V��������������Ƭ�ϣ��Ա��SƬ�����ؓ(f��)�dһ���ۙ����������IJ��Ͽ�����ͬ�����Ԝp�������`��ض�ƫ�ơ�

CTSD�ܘ�(g��u)����������������I(y��)�̓x���x���Ј��Ĵ�څ��Ҫ���ڸ��ߎ����¾���ֱ���ͽ����������ܡ����⣬�͑���ϲ�g�m���ڴֽ�Q�����Ć�һƽ�_�O(sh��)Ӌ���Ԏ��������s�����Еr�g��

CTSD�ܘ�(g��u)�������������ADC���ж�惞(y��u)�ݣ��ɞ���������l�ͷ�Cʽ�֙C���lǰ�˵ȱ�����(y��ng)�õ����x���@Щ��(y��u)�ݰ����������ɺ��ĸ��ͣ�������Ҫ���ǣ�ʹ��CTSD�܉��Q������Ҫ��ϵ�y(t��ng)���}�����ڴ����S�༼�g(sh��)ȱ�ݣ�CTSD��ʹ����ǰ���������l/�������^�͵ĄӑB(t��i)��������ˣ��߾��ȡ�������/�еȎ�����(y��ng)�õ�������Q����һֱ�Ǹ������ο�˹�������D(zhu��n)�Q����������αƽ���ADC���^�ɘ�DTSD�D(zhu��n)�Q����

Ȼ����ADI��˾���ȡ�õļ��g(sh��)ͻ���ܿ˷�֮ǰ���S�����ơ�AD7134�������CTSD�ĸ߾���ֱ����400 kHz����ADC�����Ԍ��F(xi��n)���ߵ�����Ҏ(gu��)��ͬ�r�ṩֱ�����ȣ��M���܉��Q�����܃x���x�푪(y��ng)���еĶ����P(gu��n)�I��ϵ�y(t��ng)�����}��AD7134Ҳ������һ�������ɘ������D(zhu��n)�Q��(ASRC)���܉�ͨ�^CTSD�Ĺ̶��ɘ��ٶȣ��Բ�ͬ�Ĕ�(sh��)��(j��)��(sh��)���ṩ��(sh��)��(j��)��ݔ����(sh��)��(j��)���ʿ��Բ����{(di��o)�����ɘ��l��Ӱ푣��ҿ��Դ_���ɹ�ʹ��CTSD ADC���F(xi��n)��ͬ���ȵ���������߀���������ȼ��e�`���׃ݔ����(sh��)��(j��)���ʣ��Ķ�֧���Ñ�ʹ����ɲɘӡ�

AD7134����̖會�(y��u)��

�o��B

���еĻ�B���������ˌ�����B�V�����������ɴ˜p���˽M����(sh��)������ʹ��Q�����ߴ��С������Ҫ���ǣ��c����B�V�������P(gu��n)�����܆��}������(f��)���ڣ������½���ʧ�{(di��o)�������`���λ�`��Լ�ϵ�y(t��ng)�е����ȡ�

�����t��̖�

����B�V����������(j��)���������@��������̖朵����w���t���Ƴ��V����������ȫ�����@�N���t���������s�Ĕ�(sh��)�حh(hu��n)·��(y��ng)���Ќ�ʩ�����D(zhu��n)�Q��

��ɫ����λƥ��

�o����ϵ�y(t��ng)����俹��B�V������ʹ��ͨ��ϵ�y(t��ng)����λƥ�����ܵõ��˴���������dz��m��Ҫ���ṩͨ���g��ʧ��đ�(y��ng)�ã�������ӱO(ji��n)�y�����ʜy������(sh��)��(j��)�ɼ�ģ�K���ȵȡ�

�ɿ������ɔ_

��鱾�����ОV�����ܣ�����CTSD ADC�����κ�ϵ�y(t��ng)���ɔ_���Լ�IC��(n��i)���ɔ_Ӱ푡�����DTSD ADC��SAR ADC���t���ע��p��ADC�ɘӕr�ĸɔ_�����⣬��鱾�����ОV�����ܣ������Դ��·Ҳ�����ܸɔ_��

����ݔ��

���߂�㶨������ģ�Mݔ��ͻ���(zh��n)ݔ�룬������ȫ�o����ʹ�Ì��õ��(q��)���������⣬�����c�������P(gu��n)�Ć��}������ʧ�{(di��o)�����桢��λ�`���ϵ�y(t��ng)���`��ȶ�����(f��)���ڡ�

�����O(sh��)Ӌ

����O(sh��)ӋԪ���Ĕ�(sh��)������p�٣����Ԍ��F(xi��n)�������ܵ��y��Ҳ��͡��Ķ��ɿs���O(sh��)Ӌ�r�g���ӿ�a(ch��n)Ʒ���У�����BOM����������߿ɿ��ԡ�

�ߴ�

�o��ʹ�ÿ���B�V�������(q��)�����ͻ���(zh��n)���_����ʹϵ�y(t��ng)�·��ijߴ����pС������ʹ�Ãx���x���Ŵ�����ֱ���(q��)��ADC������AD7134�������ֻ��һ�����ݔ��ADC�����Կ���ʹ�ò�փx���Ŵ���������LTC6373�������(q��)�������D14�б��^���xɢ�r�g��̖机��B�m(x��)�r�g��̖朡����Y(ji��)���@ʾ���c��Ч�xɢ�r�g��̖���ȣ��B�m(x��)�r�g��̖朿��Թ�(ji��)ʡ70%����e������dz��m�ϸ��ܶȶ�ͨ����(y��ng)�á�

�D14.�xɢ�r�g������̖机��B�m(x��)�r�g���ң���̖朱��^

�D15.�xɢ�r�g��̖机��B�m(x��)�r�g��̖朳ߴ���^

��֮��AD7134�����p�Ɍ��F(xi��n)�O(sh��)Ӌ��(d��o)�룬����sСϵ�y(t��ng)�ߴ磬������̖��O(sh��)Ӌ�����ϵ�y(t��ng)�Ŀɿ��ԣ����s�����w���Еr�g���Ҳ������;��܃x�푪(y��ng)�õ����܅���(sh��)Ҫ��

�����·

Kester, Walt. "MT-002���ο�˹��(zh��n)�t����(sh��)��(j��)�ɘ�ϵ�y(t��ng)�O(sh��)Ӌ�к����x��" ADI��˾��2009�ꡣ

Pavan, Shanti. "�B�m(x��)�r�gΔ∑�{(di��o)����ʹ���_�P(gu��n)��ݷ���DAC��ʩ��B���ơ�" IEEE�·�cϵ�y(t��ng)Փ�ļ�I����ʽՓ�ģ���58����2�ڣ�2011��2�¡�

Schreier, Richard and Gabor C. Temes. �˽�Σ-����(sh��)��(j��)�D(zhu��n)�Q���� John Wiley and Sons��2005�ꡣ

|