|

FPGA������߉��Ԫ���LCA��Logic Cell Array���@��һ������Ȳ�����������߉ģ�KCLB��Configurable Logic Block����ݔ��ݔ��ģ�KIOB��Input Output Block���̓Ȳ��B����Interconnect���������֡� �F���ɾ����T��У�FPGA���ǿɾ����������c���y߉�·���T��У���PAL��GAL��CPLD��������ȣ�FPGA���в�ͬ�ĽY����FPGA����С�Ͳ��ұ���16��1RAM���팍�F�M��߉��ÿ�����ұ��B�ӵ�һ��D�|�l����ݔ��ˣ��|�l���ف�������߉�·����I/O���ɴ˘����˼��Ɍ��F�M��߉�����ֿɌ��F�r��߉���ܵĻ���߉��Ԫģ�K���@Щģ�K�g���ý����B�������B�ӻ��B�ӵ�I/Oģ�K��FPGA��߉��ͨ�^��Ȳ��o�B�惦��Ԫ���d���̔����팍�F�ģ��惦�ڴ惦����Ԫ�е�ֵ�Q����߉��Ԫ��߉�����Լ���ģ�K֮�g��ģ�K�cI/O�g���B�ӷ�ʽ,����K�Q����߉��Ԫ��߉�����Լ���ģ�K֮�g��ģ�K�cI/O�g���ӷ�ʽ,����K�Q����FPGA���܌��F�Ĺ���, FPGA���S�o�εľ���.

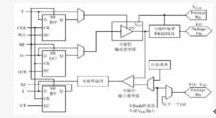

����Ŀǰ������FPGA���ǻ��ڲ��ұ����g�ģ��ѽ��h�h��������ǰ�汾�Ļ������ܣ����������˳��ù��ܣ���RAM���r犹�����DSP����Ӳ�ˣ�ASIC�ͣ�ģ�K����D1-1��ʾ��ע���D1-1ֻ��һ��ʾ��D�����H��ÿһ��ϵ�е�FPGA�����������ăȲ��Y������FPGAоƬ�� Ҫ��7������ɣ��քe�飺�ɾ���ݔ��ݔ����Ԫ�������ɾ���߉��Ԫ�������ĕr犹�����Ƕ��KʽRAM���S���IJ����YԴ����Ƕ�ĵӹ��܆�Ԫ�̓�Ƕ����Ӳ��ģ�K�� �����D1-1 FPGAоƬ�ăȲ��Y�� ����

FPGAоƬ�ăȲ��Y��

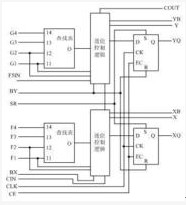

ÿ��ģ�K�Ĺ������£�����1�� �ɾ���ݔ��ݔ����Ԫ��IOB�� �����ɾ���ݔ��/ݔ����Ԫ���QI/O��Ԫ����оƬ�c����·�Ľӿڲ��֣���ɲ�ͬ늚�������ݔ��/ݔ����̖�����cƥ��Ҫ����ʾ��Y����D1-2��ʾ�� FPGA�ȵ�I/O���M���ÿ�M���܉�����֧�ֲ�ͬ��I/O�˜ʡ�ͨ�^ܛ�����`�����ã����m�䲻ͬ��늚�˜��cI/O�������ԣ������{��������Ĵ�С�����Ը�׃�ϡ�������衣Ŀǰ��I/O�ڵ��l��ҲԽ��Խ�ߣ�һЩ�߶˵�FPGAͨ�^DDR�Ĵ������g����֧�ָ��_2Gbps�Ĕ������ʡ� �����D1-2 ���͵�IOB�Ȳ��Y��ʾ��D ����

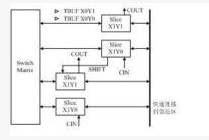

�ⲿݔ����̖����ͨ�^IOBģ�K�Ĵ惦��Ԫݔ�뵽FPGA�ăȲ���Ҳ����ֱ��ݔ��FPGA �Ȳ������ⲿݔ����̖���^IOBģ�K�Ĵ惦��Ԫݔ�뵽FPGA�Ȳ��r���䱣�֕r�g��Hold Time����Ҫ����Խ��ͣ�ͨ��Ĭ�J��0�� �������˱��ڹ������m����N����˜ʣ�FPGA��IOB�����֞����ɂ��M��bank����ÿ��bank�Ľӿژ˜�����ӿ�늉�VCCO�Q����һ��bankֻ���� һ�NVCCO������ͬbank��VCCO���Բ�ͬ��ֻ����ͬ늚�˜ʵĶ˿ڲ����B����һ��VCCO늉���ͬ�ǽӿژ˜ʵĻ����l���� ����2�� ������߉�K��CLB�� ����CLB��FPGA�ȵĻ���߉��Ԫ��CLB�Č��H���������ԕ��������IJ�ͬ����ͬ������ÿ��CLB������һ���������_�P��ꇣ��˾����4��6��ݔ�롢һЩ �x���·����·�������ȣ����|�l���M�ɡ� �_�P����Ǹ߶��`��ģ����Ԍ����M�������Ա�̎���M��߉����λ�Ĵ�����RAM����Xilinx��˾��FPGA�����У�CLB�ɶ�����һ���4����2������ͬ��Slice����߉���ɣ���D1-3��ʾ��ÿ��CLBģ�K���H�������ڌ��F�M��߉���r��߉��߀�������Þ�ֲ�ʽRAM�ͷֲ�ʽROM�� �����D1-3 ���͵�CLB�Y��ʾ��D ����

Slice��Xilinx��˾���x�Ļ���߉��λ����Ȳ��Y����D1-4��ʾ��һ��Slice�Ƀɂ�4ݔ��ĺ������Mλ߉�����g߉���惦߉�ͺ����������M�ɡ����g߉����һ�������T��XORG����һ�������c�T��MULTAND����һ�������T����ʹһ��Slice���F 2bitȫ�Ӳ����������c�T������߳˷�����Ч�ʣ��Mλ߉�Ɍ����Mλ��̖�ͺ�����������MUXC���M�ɣ����ڌ��F���ٵ����g�Ӝp��������4ݔ�뺯���l�� �����ڌ��F4ݔ��LUT���ֲ�ʽRAM��16������λ�Ĵ�����Virtex-5ϵ��оƬ��Slice�еăɂ�ݔ�뺯����6ݔ�룬���Ԍ��F6ݔ��LUT�� 64������λ�Ĵ��������Mλ߉�����ɗl�����Mλ朣��������CLBģ�K��̎���ٶȡ� �����D1-4 ���͵�4ݔ��Slice�Y��ʾ��D ����

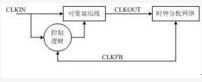

3�� ���֕r犹���ģ�K��DCM�� �����I�ȴ����FPGA���ṩ���֕r犹�����Xilinx��ȫ��FPGA�������@�N���ԣ���Xilinx�Ƴ������M��FPGA�ṩ���֕r犹�������λ�h·�i������λ�h·�i���܉��ṩ���_�ĕr犾C�ϣ����܉Ͷ��ӣ������F�^�V���ܡ� ����4�� Ƕ��ʽ�KRAM��BRAM�� ���������FPGA�����Ѓ�Ƕ�ĉKRAM���@�����չ��FPGA�đ��÷������`���ԡ��KRAM�ɱ����Þ�ζ˿�RAM���p�˿�RAM�����ݵ�ַ�惦�� ��CAM���Լ�FIFO�ȳ��ô惦�Y����RAM��FIFO�DZ��^�ռ��ĸ���ڴ˾Ͳ�������CAM�惦������Ȳ���ÿ���惦��Ԫ�ж���һ�����^߉������ CAM�еĔ������̓Ȳ���ÿһ�������M�б��^���������c�˿ڔ�����ͬ�����Д����ĵ�ַ�������·�ɵĵ�ַ���Q�����ЏV���đ��á����ˉKRAM��߀���Ԍ� FPGA�е�LUT�`������ó�RAM��ROM��FIFO�ȽY�����ڌ��H�����У�оƬ�Ȳ��KRAM�Ĕ���Ҳ���x��оƬ��һ����Ҫ���ء� ������Ƭ�KRAM��������18k���أ���λ����18���ء���Ȟ�1024�����Ը�����Ҫ��׃��λ������ȣ���Ҫ�M��ɂ�ԭ�t�����ȣ��ĺ��������λ�� ��ȣ����ܴ���18k���أ���Σ�λ������ܳ��^36���ء���Ȼ�����Ԍ���Ƭ�KRAM�������γɸ����RAM���˕rֻ������оƬ�ȉKRAM�Ĕ������� ����������ɗlԭ�t�s���� ����5�� �S���IJ����YԴ ���������YԴ�BͨFPGA�Ȳ������І�Ԫ�����B�����L�Ⱥ�ˇ�Q������̖���B���ϵ��������͂�ݔ�ٶȡ�FPGAоƬ�Ȳ������S���IJ����YԴ��������ˇ���L�ȡ����Ⱥͷֲ�λ�õIJ�ͬ�����֞�4�ͬ��e����һ���ȫ�ֲ����YԴ������оƬ�Ȳ�ȫ�֕r犺�ȫ�֏�λ/��λ�IJ������ڶ�����L���YԴ���������оƬ Bank�g�ĸ�����̖�͵ڶ�ȫ�֕r���̖�IJ�����������Ƕ̾��YԴ��������ɻ���߉��Ԫ֮�g��߉���B�Ͳ�����������Ƿֲ�ʽ�IJ����YԴ�����ڌ��Еr犡���λ�ȿ�����̖���� �����ڌ��H���OӋ�߲���Ҫֱ���x���YԴ�����ֲ��������Ԅӵظ���ݔ��߉�W�����ؓ�Y���ͼs���l���x���YԴ���Bͨ����ģ�K��Ԫ���ı��|���v�������YԴ��ʹ�÷������OӋ�ĽY�������С�ֱ�ӵ��Pϵ�� ����6�� �Ӄ�Ƕ���܆�Ԫ ������Ƕ����ģ�K��ҪָDLL��Delay Locked Loop����PLL��Phase Locked Loop����DSP��CPU��ܛ̎���ˣ�SoftCore�����F��Խ��Խ�S���ă�Ƕ���܆�Ԫ��ʹ�Æ�ƬFPGA�ɞ���ϵ�y�����OӋ���ߣ�ʹ��߂���ܛӲ�����OӋ������������SOCƽ�_�^�ɡ� ����DLL��PLL������ƵĹ��ܣ�������ɕr犸߾��ȡ��Ͷ��ӵı��l�ͷ��l���Լ�ռ�ձ��{��������ȹ��ܡ�Xilinx��˾���a��оƬ�ϼ����� DLL��Altera��˾��оƬ������PLL��Lattice��˾������оƬ��ͬ�r������PLL��DLL��PLL ��DLL����ͨ�^IP�����ɵĹ��߷�����M�й��������á�DLL�ĽY����D1-5��ʾ�� �����D1-5 ���͵�DLLģ�Kʾ��D ����

7. ��Ƕ����Ӳ�� ������Ƕ����Ӳ����������Ƕ���ܛ�˶��Եģ�ָFPGA̎�����������Ӳ�ˣ�Hard Core������Ч��ASIC�·���������FPGA���ܣ�оƬ���a����оƬ�Ȳ�������һЩ���õ�Ӳ�ˡ����磺�������FPGA�ij˷��ٶȣ�������FPGA �ж������ˌ��ó˷����������m��ͨ�ſ����c�ӿژ˜ʣ��ܶ�߶˵�FPGA�Ȳ��������˴����հl����SERDES���������_����ʮGbps���հl�ٶȡ� ����Xilinx��˾�ĸ߶ˮaƷ���H������Power PCϵ��CPU��߀��Ƕ��DSP Coreģ�K����������ϵ�y���OӋ������EDK��Platform Studio�������������Ƭ��ϵ�y��System on Chip���ĸ��ͨ�^PowerPC��Miroblaze��Picoblaze��ƽ�_���܉��_�l�˜ʵ�DSP̎�����������P���ã��_��SOC���_�lĿ �ġ�

|