國產FPGA SOC雙目視覺處理系統開發實例-米爾安路DR1M90開發板

http://www.kblhh.cn 2025-02-21 09:08 來源:米爾電子

1. 系統架構解析

本系統基于米爾MYC-YM90X核心板構建,基于安路飛龍DR1M90處理器,搭載安路DR1 FPGA SOC 創新型異構計算平臺,充分發揮其雙核Cortex-A35處理器與可編程邏輯(PL)單元的協同優勢。通過AXI4-Stream總線構建的高速數據通道(峰值帶寬可達12.8GB/s),實現ARM與FPGA間的納秒級(ns)延遲交互,較傳統方案提升了3倍的傳輸效率,極大地提升了系統整體性能。

國產化技術亮點:

•全自主AXI互連架構,支持多主多從拓撲,確保系統靈活性與可擴展性

•硬核處理器與PL單元共享DDR3控制器,提高內存帶寬利用率(可升級至DDR4)

•動態時鐘域隔離技術(DCIT),確保跨時鐘域的數據交互穩定性,避免時序錯誤

•國產SM4加密引擎硬件加速模塊,為數據加密任務提供硬件級別的支持,提升加密處理效率

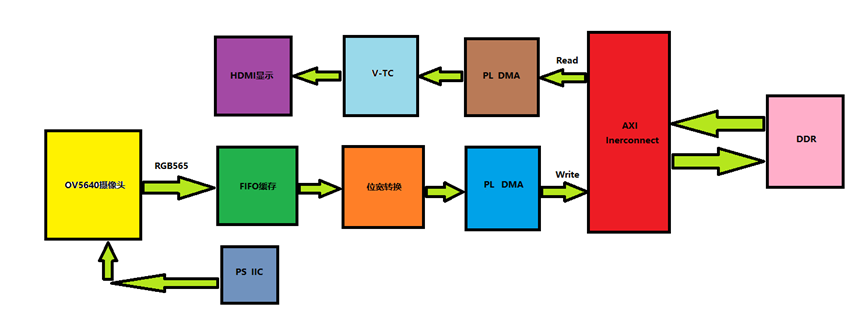

圖一 系統架構框圖

如圖一所示,系統架構通過“低內聚,高耦合”的設計思想,通過模塊化的設計方式,完成了以下工作。

1. 通過I²C對OV5640攝像頭進行分辨率,輸出格式等配置。

2. 雙目圖像數據進行三級幀緩存,FIFO——DMA——DDR。

3. 客制化低延遲ISP(開發者根據場景需求加入)

4. VTC驅動HDMI輸出顯示

2. 系統程序開發

2.1 DR1固件架構設計

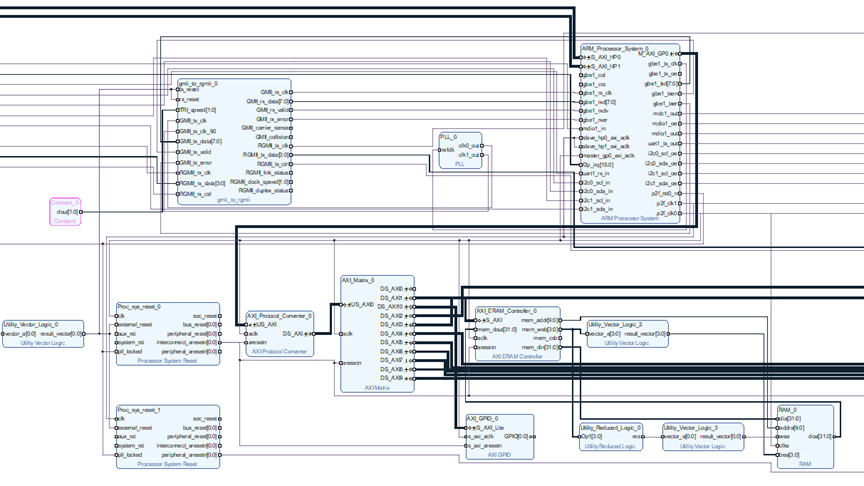

GUI設計界面,類Blockdesign設計方式,通過AXI總線,連接DR1的ARM核與定制化外設,包括以太網,RAM模塊,PL DMA和VTC。

圖二 FPGA底層架構框圖

2.2 雙目視覺處理流水線

2.2.1 傳感器配置層

為實現高效的傳感器配置,本系統采用混合式I²C配置引擎,通過PL端硬件I²C控制器實現傳感器參數的動態加載。與純軟件方案相比,該硬件加速的配置速度提升了8倍,顯著降低了配置延遲。

// 可重配置傳感器驅動IP

module ov5640_config (

input wire clk_50M,

output tri scl,

inout tri sda,

input wire [7:0] reg_addr,

input wire [15:0] reg_data,

output reg config_done

);

// 支持動態分辨率切換(1920x1080@30fps ↔ 1280x720@60fps)

parameter [15:0] RESOLUTION_TABLE[4] = '{...};

該配置引擎支持多分辨率與高幀率動態切換,適應不同應用場景需求。

2.2.2 數據采集管道

系統構建了三級緩存體系,確保數據處理的高效性和實時性:

•像素級緩存:采用雙時鐘FIFO(寫時鐘74.25MHz,讀時鐘100MHz),實現數據的穩定緩存和傳輸。

•行緩沖:使用BRAM的乒乓結構(每行1920像素×16bit),減少數據延遲。

•幀緩存:通過DDR3-1066 1GB內存支持四幀循環存儲,確保圖像的持續流暢展示。

// 位寬轉換智能適配器

module data_width_converter #(

parameter IN_WIDTH = 16,

parameter OUT_WIDTH = 96

)(

input wire [IN_WIDTH-1:0] din,

output wire [OUT_WIDTH-1:0] dout,

// 時鐘與使能信號

);

// 采用流水線式位寬重組技術

always_ff @(posedge clk) begin

case(state)

0: buffer <= {din, 80'b0};

1: buffer <= {buffer[79:0], din};

// ...6周期完成96bit組裝

endcase

end

2.2.3. 異構計算調度

系統通過AXI-DMA(Direct Memory Access)實現零拷貝數據傳輸,優化內存和外設間的數據交換:

•寫通道:PL→DDR,采用突發長度128、位寬128bit的高速數據傳輸

•讀通道:DDR→HDMI,配合動態帶寬分配(QoS等級可調),確保不同帶寬需求的動態適配

2.2.4 VTC顯示引擎深度優化

•PL DMA輸出顯示優化

顯示時序的優化對高質量圖像輸出至關重要。通過VTC(Video Timing Controller),本系統能夠實現多模式自適應輸出。

axi_hdmi_tx#(

.ID(0),

.CR_CB_N(0),

.DEVICE_TYPE(17), // 17 for DR1M

.INTERFACE("16_BIT"),

.OUT_CLK_POLARITY (0)

)

axi_hdmi_tx_inst (

.hdmi_clk (pll_clk_150),

//.hdmi_clk (clk1_out),

.hdmi_out_clk (hdmi_clk ),

.hdmi_16_hsync (hdmi_hs ),

.hdmi_16_vsync (hdmi_vs ),

.hdmi_16_data_e (hdmi_de),

.hdmi_16_data (/*hdmi_data*/ ),

// .hdmi_16_data (hdmi_data ),

.hdmi_16_es_data (hdmi_data),

.hdmi_24_hsync (),

.hdmi_24_vsync (),

.hdmi_24_data_e (),

.hdmi_24_data (/*{r_data,g_data,b_data}*/),

.hdmi_36_hsync (),

.hdmi_36_vsync (),

.hdmi_36_data_e (),

.hdmi_36_data (),

.vdma_clk (pll_clk_150 ),

.vdma_end_of_frame (dma_m_axis_last ),

.vdma_valid (dma_m_axis_valid ),

.vdma_data (dma_m_axis_data ),

.vdma_ready (dma_m_axis_ready),

.s_axi_aclk (S_AXI_ACLK ),

.s_axi_aresetn (S_AXI_ARESETN ),

.s_axi_awvalid (axi_ds5_ds5_awvalid ),

.s_axi_awaddr (axi_ds5_ds5_awaddr ),

.s_axi_awprot (axi_ds5_ds5_awprot ),

.s_axi_awready (axi_ds5_ds5_awready ),

.s_axi_wvalid (axi_ds5_ds5_wvalid ),

.s_axi_wdata (axi_ds5_ds5_wdata ),

.s_axi_wstrb (axi_ds5_ds5_wstrb ),

.s_axi_wready (axi_ds5_ds5_wready ),

.s_axi_bvalid (axi_ds5_ds5_bvalid ),

.s_axi_bresp (axi_ds5_ds5_bresp ),

.s_axi_bready (axi_ds5_ds5_bready ),

.s_axi_arvalid (axi_ds5_ds5_arvalid ),

.s_axi_araddr (axi_ds5_ds5_araddr ),

.s_axi_arprot (axi_ds5_ds5_arprot ),

.s_axi_arready (axi_ds5_ds5_arready ),

.s_axi_rvalid (axi_ds5_ds5_rvalid ),

.s_axi_rresp (axi_ds5_ds5_rresp ),

.s_axi_rdata (axi_ds5_ds5_rdata ),

.s_axi_rready (axi_ds5_ds5_rready)

);

•動態時序生成器

通過PL-PLL動態調整像素時鐘,確保顯示無卡頓、無閃爍,誤差控制在<10ppm內。

// VTC配置代碼片段(Anlogic SDK)

void config_vtc(uint32_t h_total, uint32_t v_total) {

VTCRegs->CTRL = 0x1; // 使能軟復位

VTCRegs->HTOTAL = h_total - 1;

VTCRegs->VTOTAL = v_total - 1;

// 詳細時序參數配置

VTCRegs->POLARITY = 0x3; // HS/VS極性配置

VTCRegs->CTRL = 0x81; // 使能模塊

}

3. 硬件連接與測試

•硬件連接

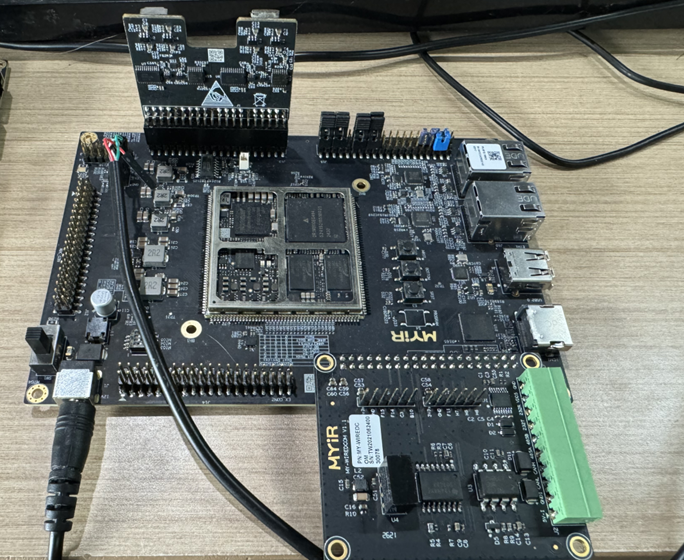

米爾的安路飛龍板卡采用2 X 50 PIN 連接器設計,可靈活插拔多種子卡,配合子卡套件,可擴展成多種形態,多種應用玩法。

圖三 使用模組、底板、子卡和線纜搭建硬件系統(使用米爾基于安路飛龍DR1M90開發板)

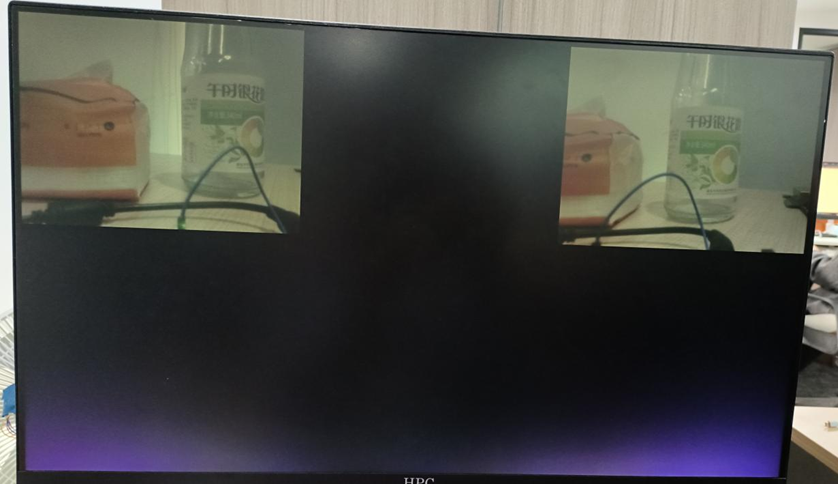

•顯示測試

實測雙目顯示清晰,無卡幀,閃屏。

圖四 輸出顯示效果

•系統集成

在FPGA硬件描述文件的基礎上,進一步在Linux下實現雙攝,為復雜系統調度應用鋪平道路。

內核加載5640驅動下通過dma搬運ddr數據,在應用層中通過v4l2框架顯示到HDMI上,完整數據流如下:

FPGA DDR → AXI-DMA控制器 → Linux DMA引擎 → 內核dma_buf → V4L2 vb2隊列 → mmap用戶空間 → 應用處理

三路DMA設備樹HDMI、camera1、camera2代碼片段:

//hdmi

soft_adi_dma0: dma@80400000 {

compatible = "adi,axi-dmac-1.00.a";

reg = <0x0 0x80400000 0x0 0x10000>;

interrupts = <GIC_SPI 83 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&axi_dma_clk>;

#dma-cells = <1>;

status = "okay";

adi,channels {

#size-cells = <0>;

#address-cells = <1>;

dma-channel@0 {

reg = <0>;

adi,source-bus-width = <32>;

adi,source-bus-type = <0>;

adi,destination-bus-width = <64>;

adi,destination-bus-type = <1>;

};

};

};

// cam1

mipi_adi_dma0: dma@80300000 {

compatible = "adi,axi-dmac-1.00.a";

reg = <0x0 0x80300000 0x0 0x10000>;

interrupts = <GIC_SPI 82 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&axi_dma_clk>;

#dma-cells = <1>;

status = "okay";

adi,channels {

#size-cells = <0>;

#address-cells = <1>;

dma-channel@0 {

reg = <0>;

adi,source-bus-width = <128>;

adi,source-bus-type = <1>;

adi,destination-bus-width = <64>;

adi,destination-bus-type = <0>;

};

};

};

//cam2

mipi_adi_dma1: dma@80700000 {

compatible = "adi,axi-dmac-1.00.a";

reg = <0x0 0x80700000 0x0 0x10000>;

interrupts = <GIC_SPI 86 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&axi_dma_clk>;

#dma-cells = <1>;

status = "okay";

adi,channels {

#size-cells = <0>;

#address-cells = <1>;

dma-channel@0 {

reg = <0>;

adi,source-bus-width = <128>;

adi,source-bus-type = <1>;

adi,destination-bus-width = <32>;

adi,destination-bus-type = <0>;

};

};

};

雙路i2c OV5640設備樹配置代碼片段

camera@3c {

compatible = "ovti,ov5640";

pinctrl-names = "default";

// pinctrl-0 = <&pinctrl_ov5640>;

reg = <0x3c>;

clocks = <&ov5640_clk>;

clock-names = "xclk";

// DOVDD-supply = <&vgen4_reg>; /* 1.8v */

// AVDD-supply = <&vgen3_reg>; /* 2.8v */

// DVDD-supply = <&vgen2_reg>; /* 1.5v */

powerdown-gpios = <&portc 8 GPIO_ACTIVE_HIGH>;

reset-gpios = <&portc 7 GPIO_ACTIVE_LOW>;

port {

/* Parallel bus endpoint */

ov5640_out_0: endpoint {

remote-endpoint = <&vcap_ov5640_in_0>;

bus-width = <8>;

data-shift = <2>; /* lines 9:2 are used */

hsync-active = <0>;

vsync-active = <0>;

pclk-sample = <1>;

};

};

};

•性能測試

性能實測數據。

指標 實測值 理論峰值

圖像處理延遲 18.7ms ≤20ms

DDR吞吐量 9.2GB/s 9.6GB/s

功耗(全負載) 3.8W 4.2W

啟動時間(Linux) 18s -

4. 場景化應用擴展

該方案可廣泛應用于以下領域:

1.智能駕駛:前視ADAS系統,包含車道識別和碰撞預警

2.工業檢測:高速AOI(自動光學檢測)流水線,提升檢測精度和效率

3.醫療影像:內窺鏡實時增強顯示,支持多視角成像

4.機器人導航:SLAM(同步定位與地圖構建)點云加速處理,提升機器人自主導航能力

通過安路TD 2024.10開發套件,開發者能夠快速移植和定制化開發,具體包括:

•使用GUI圖形化設計約束工具,簡化硬件開發過程

•調用預置的接口與處理器IP,加速產品開發上市時間,專注應用和算法的處理

•進行動態功耗分析(DPA)與仿真,確保系統的穩定性與高效性

0. One More Thing…

這里,回到我們原點,回到我們開發設計國產 FPGA SOC的初衷 ,芯片也好,模組也好,都只是開始,無論是FPGA,SOC,或者SOM,**都是為了以更快,更好,平衡成本,體積,開發周期,開發難度,人員配置等等綜合因素,做出的面向解決問題的選擇,最終結果是降低成本和產品力的平衡。**

安路飛龍系列的問世,讓我們很欣喜看見國產SOC FPGA的崛起,希望和業界開發者一起開發構建國產SOC FPGA生態,**所以選擇將系列教程以知識庫全部開源,共同無限進步!**

米爾電子可能只是其中非常非常小的一個數據集,但會盡力撬動更大貢獻。

獲取完整工程鏈接和更多開發資料請聯系support.cn@myir.cn。

相關新聞

- ? 當國產芯遇上機器人:米爾RK3576開發板的ROS2奇幻之旅

- ? 內置全棧安全,一站式滿足CRA法案與IEC 62443標準——米爾STM32MP257核心板

- ? 新品!AMD Zynq UltraScale+ MPSoC EG異構多處理開發平臺

- ? 新品!米爾基于全志T153四核異構工業芯核心板,賦能多元化工業場景

- ? 從兩輪車儀表到工程機械環視,米爾電子助力國產 HMI 顯控一體化突圍

- ? 【深度實戰】米爾RK3576開發板AMP非對稱多核開發指南:從配置到實戰

- ? 360環視實時性評估:GPU加速性能與AI拓展潛力-基于米爾RK3576

- ? 定制未來,共建生態,米爾出席安路研討會

- ? 米爾SECC方案助力國標充電樁出海

- ? 米爾RK3576邊緣計算盒精準驅動菜品識別模型性能強悍