PCIe 5.0產(chǎn)品測試驗(yàn)證火熱進(jìn)行中,為未來引領(lǐng)消費(fèi)者市場做好準(zhǔn)備

http://www.kblhh.cn 2022-04-28 17:13 來源:益萊儲

—— 益萊儲為PCIe 5.0開發(fā)客戶提供預(yù)算靈活、快速供貨的測試方案

讓PCIe總線保證足夠的帶寬、供電也成為了不斷追求的目標(biāo),對更高速度的需求推動了標(biāo)準(zhǔn)機(jī)構(gòu)定義下一代PCI Express,PCIe 5.0速度從PCIe 4.0 的16GT /s翻倍至32 GT /s ;到了剛發(fā)布的PCIe 6.0,實(shí)現(xiàn)了帶寬速率全面翻倍,而且PCIe 6.0對底層信令進(jìn)行了改進(jìn)。

是德科技剛剛發(fā)布了針對PCIe 5.0/6.0的完整測試方案,至此能夠提供全方位的物理層測試解決方案,成為目前僅有的完整提供從建模、仿真、互連參數(shù)表征、Tx、PLL 和 Rx 測試解決方案的公司。通過是德科技租賃合作伙伴益萊儲/Electro Rent的聯(lián)合支持,客戶可以以測試儀器購買價(jià)格的一小部分、找到最新的產(chǎn)品,并以最快的速度獲得。在最近跟需要PCIe 5.0測試方案的客戶的互動中,我們深切感受到來自客戶的急迫需求和對我們服務(wù)的欣慰,同心協(xié)力幫助客戶贏得未來市場先機(jī)。

向下一代PCIe標(biāo)準(zhǔn)的演進(jìn)

PCI Express 5.0代表了使用非歸零(NRZ)信令的最新PCI標(biāo)準(zhǔn),速度從PCIe 4.0 的16GT /s翻倍至32 GT /s,PCIe 5.0標(biāo)準(zhǔn)在2019年完成。為了應(yīng)對日益增長的高性能計(jì)算、人工智能加速器、高性能存儲等快速發(fā)展的需求,PCI-SIG著手開發(fā)制定下一代PCIe 6.0規(guī)范,PCIe 6.0 v1.0版本規(guī)范上已于2022年1月正式發(fā)布。

PCIe 6.0擁有了超低延遲、超高帶寬、超快速率,而且PCIe 6.0對底層信令進(jìn)行了改進(jìn),也是PCIe 歷史上改進(jìn)最大的一次。通過PCIe鏈路速度提升一倍,PCIe 6.0在實(shí)際上獲得了帶寬速率全面翻倍的效果,x1通道從4GB/s提升到了8GB/s,x16通道則一直擴(kuò)展到了單向128GB/s,雙向達(dá)到256GB/s。這相當(dāng)于設(shè)備可以使用更少的通道數(shù)量,達(dá)到更高的速率,從而獲得實(shí)現(xiàn)降低硬件成本效果。

雖然PCIe 6.0相關(guān)標(biāo)準(zhǔn)已經(jīng)發(fā)布,但不可否認(rèn)從消費(fèi)者市場來看,PCIe 5.0市場還處于早期階段。大部分消費(fèi)者還停留在PCIe 4.0,主要是因?yàn)槟壳爸С諴CIe 5.0的產(chǎn)品價(jià)格都十分高昂,對消費(fèi)者而言,PCIe 4.0并不會影響工作和游戲體驗(yàn),因此PCIe 5.0的普及率還比較低。不過PCIe 5.0相關(guān)產(chǎn)品的測試驗(yàn)證正在火熱進(jìn)行中。

新一代PCIe 5.0測試的挑戰(zhàn)

PCIe 5.0測試挑戰(zhàn)隨著速度翻倍而增加,最大挑戰(zhàn)來自于通道長度,信號速度越快,在PC板上傳輸?shù)男盘栞d頻越高。有兩類物理損傷會限制工程師傳輸PCIe信號的預(yù)期距離:一個是通道的衰減,一個是由于管腳、連接器、通孔和其他結(jié)構(gòu)中發(fā)現(xiàn)的阻抗不連續(xù)而在通道內(nèi)發(fā)生的反射。

PCIe 5.0規(guī)范使用的信道在16 GHz時衰減為-36分貝,16 GHz的頻率代表32 GT/s數(shù)字信號的奈奎斯特頻率。例如,當(dāng)PCIe 5.0信號開始時,它可能具有800 mV的典型峰間電壓。然而,在通過建議的-36分貝通道后,就找不到任何與睜開眼睛的相似之處。只有通過應(yīng)用基于發(fā)射機(jī)的均衡(去加重)和接收機(jī)均衡(CTLE和DFE的組合),PCIe 5.0信號才能通過系統(tǒng)通道并被接收機(jī)準(zhǔn)確地解釋。

對于PCIe 5.0信號,眼睛高度的最低預(yù)期為10 mV(均衡后)。即使有一個近乎完美的低抖動發(fā)射器,信道的顯著衰減也會降低信號振幅,以至于由反射和串?dāng)_引起的任何其他類型的信號損傷都會關(guān)閉可恢復(fù)眼。

為了幫助確保支持PCIe 5.0的產(chǎn)品取得成功,是德科技積極提供測試解決方案。在物理層系統(tǒng)仿真、物理層互連以及發(fā)射端(Tx)和接收端(Rx)測試基礎(chǔ)上,又最新增加了PCIE5.0協(xié)議分析測試方案,至此能夠提供從設(shè)計(jì)仿真到物理層再到協(xié)議層的測試和驗(yàn)證。

UXR+M8040 PCIe 5.0測試升級平臺

是德科技UXR0334A+M8040A 實(shí)現(xiàn)了PCIe 5.0高速接口測試平臺升級,這也是益萊儲客戶最近的熱門需求。

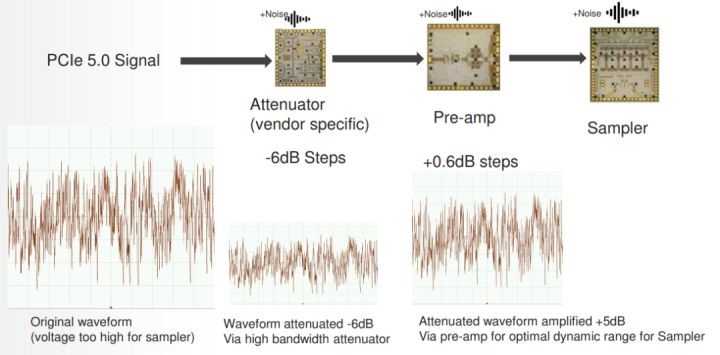

信號進(jìn)入示波器后,經(jīng)過模擬前端包括衰減器、放大器、采樣器,再進(jìn)入到 ADC,示波器中所使用的半導(dǎo)體工藝、封裝設(shè)計(jì)、互連設(shè)計(jì),ADC 的垂直有效位數(shù)等的差異,會導(dǎo)致信噪比會存在差距。所以,降低儀器底噪、提升 ADC 的位數(shù)會為提升測量精度帶來非常大的幫助,在足夠采樣率的條件下,這些性能超過了采用更高采樣率對測量結(jié)果的影響。

圖1 示波器前端信號采集鏈路

基于 InP HB2C 工藝 MMIC 前端、多芯片三維封裝互連和 10bit ADC UXR系列示波器在 PCIe 5.0 的基于 1e-12 條件下的眼高、眼寬、TJ 等結(jié)果有明顯更高的裕量。以33GHz帶寬的UXR0334A示波器為例,在相同垂直滿量程的條件下,UXR的底噪指標(biāo)是同行33GHz帶寬示波器的一半水平。

另外從測量方法上來說,垂直刻度的設(shè)定會影響到測量的信噪比,測量時有一點(diǎn)比較重要的是,要優(yōu)化垂直刻度,讓信號盡量充滿垂直滿量程,這樣會達(dá)到最佳的測量信噪比。從下表中可以看到,在相同的測試條件下:使用 M8040A誤碼儀,加入一定的壓力,經(jīng)過 PCIe 5.0 Base夾具構(gòu)建的36dB的損耗,設(shè)置相同的 Preset P9,使用相同的接收 CTLE DC Gain 10dB,示波器都優(yōu)化調(diào)整了垂直刻度。

M8040A 高性能 BERT 是一款高度綜合的比特誤碼率測試儀(BERT),M8040A 專為研發(fā)和測試工程師設(shè)計(jì),幫助他們表征芯片、器件、收發(fā)信機(jī)模塊和子組件、電路板以及系統(tǒng)。不僅能夠測試 PCIe 5.0,還能為新興的 PCIe 6.0技術(shù)探索發(fā)展路線,適用于物理層表征和合規(guī)性測試,它支持 PAM4 和 NRZ 信號,以及高達(dá) 64 GBaud 的數(shù)據(jù)速率,覆蓋 400 GbE 標(biāo)準(zhǔn)的所有特性。

相關(guān)新聞

- ? 面向“工業(yè)5.0”的產(chǎn)業(yè)互聯(lián)網(wǎng)平臺發(fā)展

- ? 如何在制造業(yè)中使用工業(yè)5.0以及面臨的挑戰(zhàn)

- ? 工業(yè)5.0開啟,在不拼規(guī)模、拼組織的時代,中國制造業(yè)的優(yōu)勢如何保持?

- ? 工業(yè)5.0:為何是下一個10年的制造業(yè)關(guān)鍵性變革方向?

- ? 歐盟“工業(yè)5.0”對我國制造業(yè)高質(zhì)量發(fā)展的影響與啟示丨基于智庫雙螺旋法的應(yīng)用探索研究

- ? 歐盟“工業(yè)5.0”對我國制造業(yè)高質(zhì)量發(fā)展的影響與啟示

- ? 五大數(shù)字化發(fā)展趨勢將在未來十年推動制造業(yè)加速邁向工業(yè)5.0時代

- ? 校企合作,深圳技術(shù)大學(xué)聯(lián)合高川自動化成立智能控制實(shí)驗(yàn)室

- ? 賦能數(shù)字化轉(zhuǎn)型和設(shè)備運(yùn)維,福祿克測試方案2020年將會給業(yè)界帶來哪些驚喜?

- ? 凌華科技發(fā)布PCIe-GIE72/74 GigE Vision PoE+圖像采集卡

編輯精選

- ? 賦能綠色智造 臺達(dá)與長三角制造企業(yè)探討智造新路徑

- ? 2025 年伺服電機(jī)行業(yè)產(chǎn)業(yè)布局深度解析

- ? HMS行業(yè)洞察:2025工業(yè)網(wǎng)絡(luò)市場全景解讀

- ? 總投資15億元!ABB超級工廠落子南京

- ? 構(gòu)筑工業(yè) AI 時代的數(shù)據(jù)底座,藍(lán)卓supOS X工廠操作系統(tǒng)全球首發(fā)

- ? CC-Link協(xié)議家族與會員單位集中亮相,共話行業(yè)新發(fā)展

- ? 2025 工業(yè)操作系統(tǒng)大會在蘇州隆重開幕

- ? 創(chuàng)新、落地、增效:施耐德電氣以AI賦能產(chǎn)業(yè)新生態(tài)

- ? 西門子2026 年數(shù)字化程度展望

- ? 國家統(tǒng)計(jì)局:11月工業(yè)機(jī)器人產(chǎn)量增長超20%

工控原創(chuàng)

- ? “人工智能+制造”怎么推進(jìn)?工信部等八部門印發(fā)專項(xiàng)行動實(shí)施意見

- ? 經(jīng)典煥新,實(shí)力躍升:西門子 S7-200 SMART G2 系列正式登場

- ? 波士頓動力發(fā)布企業(yè)級Atlas機(jī)器人,攜手DeepMind賦能工業(yè)新未來

- ? 12 月工業(yè)自動化月度焦點(diǎn)回顧,辭舊迎新啟新程!

- ? 統(tǒng)一以太網(wǎng)標(biāo)準(zhǔn)再迎里程碑,SPE 和 Ethernet-APL 解鎖工業(yè)數(shù)字化新機(jī)遇

- ? 11月RatingDog中國制造業(yè)PMI降至49.9,供需走弱重回收縮區(qū)間

- ? 11月工控圈發(fā)生了這些矚目的大事件

- ? 十月工控領(lǐng)域重要資訊,一睹為快!

- ? 回顧 | 以技術(shù)干貨 + 落地案例,解鎖產(chǎn)業(yè)升級新路徑

- ? ABB報(bào)告:工業(yè)停機(jī)每小時損失高達(dá)50萬美元,知行鴻溝阻礙現(xiàn)代化更新