秦曉的“國企觀”

http://www.kblhh.cn 2009-07-21 17:25 來源:中國自動化學會專家咨詢工作委員會

摘要:與傳統(tǒng)的PLC、PAC以及基于PC的系統(tǒng)控制技術不同,嵌入式控制技術可以根據(jù)受控對象不同,為我們提供多種選擇。微控制器是嵌入式控制技術中最廣為人知的一項,而本文將向你展示ASIC和FPGA技術所具有的一些獨特優(yōu)勢。

與傳統(tǒng)的PLC、PAC以及基于PC的系統(tǒng)控制技術不同,嵌入式控制技術可以根據(jù)受控對象不同,為我們提供多種選擇。微控制器是嵌入式控制技術中最廣為人知的一項,而本文將向你展示ASIC和FPGA技術所具有的一些獨特優(yōu)勢。

嵌入式控制系統(tǒng)不同于數(shù)據(jù)采集系統(tǒng)以及那些只針對標準大眾化產(chǎn)品的控制系統(tǒng)。它可以復雜到類似一套電信交換系統(tǒng),也可以如一套警報系統(tǒng)。在不同的應用中,我們可以采用多種方案來滿足不同要求。哪種方案最適合你,一方面由最終的使用情況決定,另一方面取決于系統(tǒng)生命周期。

有三種CPU方案用在嵌入式系統(tǒng)中最為合適。它們分別是:微控制器、現(xiàn)場可編程邏輯門陣列(FPGA)以及專用集成電路(ASIC)。

微控制器的最大優(yōu)點是它們的高度適應性。開發(fā)人員可以通過C以及C++之類的高級語言對它們實施編程。如今,許多微控制器應用已經(jīng)相當復雜了,以至于我們能夠采用Linux或Microsoft Windows Embedded之類的操作系統(tǒng)。

微控制器的高度適應性同時也成為了它們最大的缺陷。微控制器往往需要搭配一套編寫復雜、資源全面的操作系統(tǒng)方能使用。在許多應用中,微控制器無法勝任那些對性能要求極高的任務。

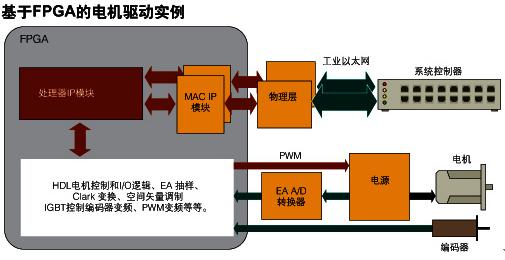

嵌入式控制系統(tǒng)設計師可以利用FPGA和ASIC實現(xiàn)一些非常復雜的算法。這些算法會在結構緊湊的可編程硬件內高速運行。

ASIC和FPGA的特點

如今,我們還可以用另外兩種具有計算功能的芯片替代微控制器。它們分別是現(xiàn)場可編程邏輯門陣列(FPGA)以及專用集成電路(ASIC)。兩者的共同特點首先是都采用了硬件化的布爾邏輯算法。其次,它們都具有高度的適應性,能夠實現(xiàn)相當豐富的邏輯功能。這些功能小到簡單的開關控制,大到整個微處理器。再者,它們都可以通過諸如VHDL和Verilog之類的標準硬件描述語言(HDL)進行編程,不必動用由第三代或更高級編程語言編寫的軟件進行編程。

兩者的不同之處在于一次性工程成本(NRE)和可變成本,以及重復編程性、可測量性、開發(fā)時間(與產(chǎn)量有關)等方面。

FPGA的特點是能夠被重復編程,從而為樣品開發(fā)提供了便利。此外,我們還能夠對FPGA進行產(chǎn)生調整和現(xiàn)場升級,從而加快了產(chǎn)品投放市場的速度。一款FPGA平臺適用于多種產(chǎn)品,從而起到了平衡開發(fā)成本與資源的作用。如果我們采用ASIC或MCU作設計開發(fā),那么就無法得到這些優(yōu)勢了。

維基百科把FPGA描述成一種包含了可編程邏輯器件(被稱為“邏輯模塊”)以及可編程互連網(wǎng)絡的半導體設備。邏輯模塊經(jīng)過編程后能夠實現(xiàn)基本的邏輯門功能,例如與邏輯(AND)和異或邏輯(XOR),以及更復雜的復合邏輯功能,例如解碼器或數(shù)學運算功能。

ASIC是一種針對某種特殊應用定制的集成電路,它不具有通用性。例如,一款經(jīng)過專門設計、用來實現(xiàn)手機中某項特定功能的芯片就是一種ASIC。

在設計一款全定制ASIC時,我們必須繪制出設備的整個光刻層。ASIC技術的NRE大部分消耗在將HDL代碼轉換為半導體結構階段。

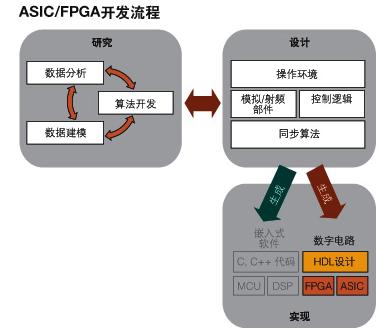

無論是設計FPGA還是ASIC,都要先從編寫硬件描述語言(HDL)起步。但是在編寫HDL代碼之前,我們最好采用軟件或硬件仿真的方式來構建、測試并調試整個系統(tǒng)的算法。

算法的開發(fā)過程

一般而言,算法最初是作為一種系統(tǒng)工程策略,由用戶提出的使用要求所決定。

以一個機器人割草機為例。整個開發(fā)項目可能會從一次完整的計算機仿真開始。其中,處于開發(fā)階段的算法(AUD)是由C或C++程序模塊組合而成的。 這些模塊可能是借用了其他項目的開發(fā)成果,也可能是通過另外的多種途徑獲得的。

這些模塊由一套專門的監(jiān)控程序調用。監(jiān)控程序的作用是對嵌入式系統(tǒng)軟件實行打包操作。它可以在桌面開發(fā)系統(tǒng)上運行,而且桌面系統(tǒng)還可以同時運行電機、驅動器、傳感器以及圖形用戶界面的的C或C++仿真模塊。

算法開發(fā)從一開始就是在計算機上進行的,從而保證算法能夠完成預訂的功能并且時刻處于開發(fā)人員的掌控之中。每一位明智的開發(fā)人員都會在確保算法正確,并且不會出現(xiàn)潛在硬件隱患的情況下將它移交給測試工程師。否則,你最終得到的將是一臺失控的機器人,就像科幻小說中描述的那樣。簡直就是測試工程101!

一旦算法被證明能夠執(zhí)行正確的操作,系統(tǒng)開發(fā)人員就可以將它下載到第一部機器人割草機樣機中,并且對它作一系列測試,以便開發(fā)硬件平臺。對硬件開發(fā)程序而言,算法在其中扮演了機器人測試向導的角色。

硬件子系統(tǒng)可能已經(jīng)經(jīng)過了基于PC的數(shù)據(jù)采集系統(tǒng)和控制系統(tǒng)的測試。但是,這些系統(tǒng)中的測試程序與AUD相比,只是擁有相同的硬件接口規(guī)范而已,在其他方面不具有相似性。而且,各個硬件子系統(tǒng)可能還沒有協(xié)同工作過。因此,系統(tǒng)開發(fā)的最后一個步驟就是整合所有的子系統(tǒng),并且統(tǒng)一調試。

系統(tǒng)集成最初可能是從在嵌入式單板計算機(SBC)上運行AUD開始的。這種計算機上運行的其實是用高級語言編寫,并經(jīng)過硬件仿真調試的相同程序。這是AUD首次對實際硬件實行控制。

這一階段,許多軟硬件接口以及軟硬件自身的問題都會暴露出來。在嵌入式控制系統(tǒng)中,硬件與軟件的關系非常緊密,以至于任何一處硬件或軟件的改動都可能影響到對方。正是由于SBC具有機動性和可重復編程的特點,我們才選中它來實現(xiàn)完整的系統(tǒng)調試。

嵌入式控制系統(tǒng)設計師可以先利用FPGA對硬件設計作調試。然后,在產(chǎn)品產(chǎn)量允許的前提下,轉而使用定制ASIC。

硬件實現(xiàn)

在我們解決了所有軟件和硬件問題之后,就可以推出一款在外觀和功能上都與最終產(chǎn)品十分接近的樣品。ASIC與FPGA需要相同的引腳分布,它們都會被安裝到一塊小型母板上。母板可以支持任意一款引腳位置與之吻合的芯片。

如果我們采用FPGA,那么就需要在母板上額外增加一塊程序存儲芯片。這塊芯片內存儲了FPGA內部的互聯(lián)信息。當我們把AUD下載到硬件之后,就會形成這些信息。FP

GA采用了動態(tài)RAM技術。這種技術的致命缺陷是具有易失性,F(xiàn)PGA內部運行的程序在斷電之后會全部丟失。

這一階段,系統(tǒng)開發(fā)人員可能會采用FPGA進行設計。因為FPGA版本的控制模塊在引腳分布上可以做到與ASIC版本一致,而且FPGA還具有可重復編程的特點。FPGA的致命弱點同時也是它最受青睞的地方。因為在系統(tǒng)投入現(xiàn)場應用之前,開發(fā)人員很可能會對軟件作升級。這樣的話,如果我們只是為了升級ASIC程序就開發(fā)一款新產(chǎn)品,這樣做在成本方面顯然是行不通的。

即使我們的設計最終成為了一款產(chǎn)量達到千位數(shù)的標準產(chǎn)品,F(xiàn)PGA在經(jīng)濟性方面仍然具有優(yōu)勢。只有在產(chǎn)量達到幾百萬甚至更多的情況下,將AUD轉換到ASIC所產(chǎn)生的大量NRE投入才可能被補償?shù)簟.斎唬瑢τ谙M類產(chǎn)品而言,這樣的產(chǎn)量很快就能達到。

把AUD轉換為適用于FPGA的HDL程序可能很困難也可能很簡單。這一方面要看我們采用什么工具將已有的經(jīng)過調試的軟件轉換為指定硬件的HDL代碼,另一方面要看這種轉換是在哪一階段完成的。

例如,Mathworks正在與ASIC、FPGA供應商合作開發(fā)一套工具,幫助工程師將那些采用Matlab與Simulink編寫的AUD代碼轉換為HDL,另有一些工具能夠將C和C++代碼轉換為HDL。

當然,基本的測試表明,系統(tǒng)在經(jīng)歷任何重大改變之后,都必須重新作一遍開發(fā)測試。為了確保FPGA芯片下載了HDL代碼之后確實能夠執(zhí)行原始AUD所指定的操作,我們必須做仿真和測試。當我們從FPGA編程轉換到定制ASIC設計時,也會面臨同樣的問題。

翻譯:翁思健

相關新聞

- ? 工業(yè)自動化核心引擎:PLC控制器行業(yè)現(xiàn)狀、供需格局與未來趨勢深度剖析

- ? 國家級標準落地|臺達參與編制PLC編程語言應用導則正式發(fā)布

- ? 絲滑遷移、無痛替代!科遠PLC自動化平臺,破解國產(chǎn)替代核心難題!

- ? 新型工業(yè)控制測試床正式發(fā)布

- ? 繁易的戰(zhàn)略進擊:從HMI到PLC,走向全棧式自動化融合創(chuàng)新

- ? 中控技術PLC助力全球最大26MW海上風電機組順利安裝

- ? 破局外資主導,中國大型PLC國產(chǎn)化提速

- ? 國產(chǎn)工業(yè)“大腦”擔綱指揮!寶信軟件天行T4實現(xiàn)規(guī)模化應用

- ? 信捷電氣小型PLC 繼續(xù)穩(wěn)居國產(chǎn)品牌第一

- ? 斯巴魯工廠測試全固態(tài)電池,用于工業(yè)機器人和PLC

編輯精選

- ? 賦能綠色智造 臺達與長三角制造企業(yè)探討智造新路徑

- ? 2025 年伺服電機行業(yè)產(chǎn)業(yè)布局深度解析

- ? HMS行業(yè)洞察:2025工業(yè)網(wǎng)絡市場全景解讀

- ? 總投資15億元!ABB超級工廠落子南京

- ? 構筑工業(yè) AI 時代的數(shù)據(jù)底座,藍卓supOS X工廠操作系統(tǒng)全球首發(fā)

- ? CC-Link協(xié)議家族與會員單位集中亮相,共話行業(yè)新發(fā)展

- ? 2025 工業(yè)操作系統(tǒng)大會在蘇州隆重開幕

- ? 創(chuàng)新、落地、增效:施耐德電氣以AI賦能產(chǎn)業(yè)新生態(tài)

- ? 西門子2026 年數(shù)字化程度展望

- ? 國家統(tǒng)計局:11月工業(yè)機器人產(chǎn)量增長超20%

工控原創(chuàng)

- ? “人工智能+制造”怎么推進?工信部等八部門印發(fā)專項行動實施意見

- ? 經(jīng)典煥新,實力躍升:西門子 S7-200 SMART G2 系列正式登場

- ? 波士頓動力發(fā)布企業(yè)級Atlas機器人,攜手DeepMind賦能工業(yè)新未來

- ? 12 月工業(yè)自動化月度焦點回顧,辭舊迎新啟新程!

- ? 統(tǒng)一以太網(wǎng)標準再迎里程碑,SPE 和 Ethernet-APL 解鎖工業(yè)數(shù)字化新機遇

- ? 11月RatingDog中國制造業(yè)PMI降至49.9,供需走弱重回收縮區(qū)間

- ? 11月工控圈發(fā)生了這些矚目的大事件

- ? 十月工控領域重要資訊,一睹為快!

- ? 回顧 | 以技術干貨 + 落地案例,解鎖產(chǎn)業(yè)升級新路徑

- ? ABB報告:工業(yè)停機每小時損失高達50萬美元,知行鴻溝阻礙現(xiàn)代化更新